# SOME NEW OPERATIONAL TRANSRESISTANCE AMPLIFIER BASED SINUSOIDAL/SQUARE WAVEFORM GENERATORS

#### A THESIS

submitted by

#### CHANDRA SHAKER PITTALA

for the award of the degree

of

#### DOCTOR OF PHILOSOPHY

(Estd u/s 3 of UGC Act of 1956)

DEPARTMENT OF ELECTRONICS AND COMMINICATION ENGINEERING VFSTR UNIVERSITY, VADLAMUDI GUNTUR – 522213, ANDHRA PRADESH, INDIA

OCTOBER 2016

**Dedicated**

to

My family

#### **DECLARATION**

I hereby declare that the work reported in the Ph.D. thesis entitled "SOME NEW OPERATIONAL TRANSRESISTANCE AMPLIFIER BASED SINUSOIDAL/SQUARE WAVEFORM GENERATORS" submitted at Vignan's Foundation for Science, Technology and Research University, Vadlamudi, India, is an authentic record of my work carried out under the supervision of Prof. Avireni Srinivasulu. I have not submitted this work elsewhere for any other degree or diploma.

(CHANDRA SHEKAR PITTALA)

THESIS CERTIFICATE

This is to certify that the thesis entitled SOME NEW OPERATIONAL

TRANSRESISTANCE AMPLIFIER BASED SINUSOIDAL/SQUARE

WAVEFORM GENERATORS submitted by CHANDRA SHAKER

PITTALA to the Vignan's University, Vadlamudi, Guntur, for the award of the

degree of **Doctor of Philosophy** is a bonafide record of the research work done by

him under my supervision. The contents of this thesis, in full or in parts, have not

been submitted to any other Institute or University for the award of any degree or

diploma.

Prof. Avireni Srinivasulu

Research Guide

Professor, Dept. of Electronics and Communication Engineering

Vignan's University, Andhra Pradesh, India

Date:

Place: Guntur

#### **ACKNOWLEDGEMENT**

I would like to acknowledge my deep sense of gratitude to my supervisor **Dr. Avireni Srinivasulu**, Department of Electronics and Communication Engineering, Vignan's Foundation for Science, Technology and Research University, Vadlamudi, Guntur, for his constant valuable guidance and encouragement. He gladly accepted all the pains in going through my work again and again, and giving me opportunity to learn essential research skills. His ability to quickly understand the depth of the problem and suggesting a clear solution has always surprised me. This thesis would not have been possible without his insightful and critical suggestions, his active participation in constructing right models and a very supportive attitude. I will always remain grateful to him for giving direction to my life.

I express my sincere thanks to **Dr. C. Thangaraj**, Vice Chancellor, **Dr. B. Ramamoorthy**, Rector, **Dr. N. Usha Rani**, Head of the Department of Electronics and Communication Engineering, for providing the necessary facilities for carrying out the research work. I would like to thank the doctoral committee panel, **Dr. P. Subbaraj**, **Dr. M. S. S. Rukmini**, **Dr. Venkateswarlu** and **Dr. N. Ramraj** for providing me with their suggestions.

I would like to thank teaching and non-teaching staff members of Department of E.C.E who have been kind enough to advise and help in their respective roles.

I would like to express my heartiest thanks to my colleague **Mr. V. Vijay** for valuable comments, suggestions and discussions. I am grateful to **Mr. Y. Samrat** for his uncountable help during the hardware implementation in Cadence lab despite of his numerous duties and busy schedule.

I would like to acknowledge the support of my parents, **Kamala** and **Venkati**, and my sisters **Raja kumari**, **Uma Rani** and **Usha Rani** for their continuing support and encouragement.

### P. Chandra Shaker

#### **ABSTRACT**

## SOME NEW OPERATIONAL TRANS-RESISTANCE AMPLIFIER BASED SINUSOIDAL/SQUARE WAVEFORM GENERATORS

KEYWORDS: Analogue signal processing blocks, Duty cycles, Operational transresistance amplifier, Oscillators, Square waveform generators, Waveform generators.

Waveform generators have wide range of applications in numerous electronic devices, including electronic instruments, measurement systems, telecommunications, power conversion control circuits and signal processing applications. Several waveform generator circuits have existed in the literature based on operational amplifier (op-amp) as a main active element. However, these circuits are not able to operate at high frequency due to fixed gain bandwidth product and less slew rate.

To conquer the above disadvantages several circuits have been presented in the literature based on current-mode devices. When wide bandwidth, low power consumption and low voltage operation are needed simultaneously, current mode devices are preferred rather than voltage mode devices. Current mode circuits feature the advantage of high bandwidth, better linearity, larger dynamic range and non-interference between the gain and bandwidth.

In recent past, an active current mode device operational transresistance amplifier (OTRA) has made considerable attention of the analog IC designers. OTRA is a three terminal active device. Several implementations have emerged using OTRA such as Voltage Gain Amplifiers (VGAs), filters, Proportional Integral and Derivative (PID) controllers, analogue multiplier, immitance simulators, oscillators and waveform generators.

Sinusoidal waveform generators with independent control of condition of oscillation and frequency of oscillation play an important role in communications and signal processing application. It has also been seen that the OTRA is very useful as an analogue building block and receiving regular attention in waveform generators, oscillators, and design of amplifiers and filters. The OTRA provides a constant bandwidth virtually independent of the gain. Characterized by low input and output

impedances, it leads to circuits that are insensitive to stray capacitances, providing current processing at the input terminal which are virtually grounded.

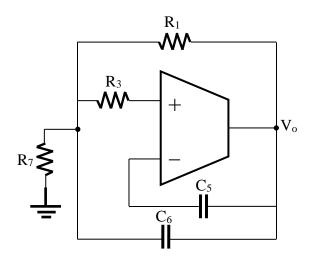

In this thesis, a generalized configuration with a grounded passive component is proposed to realize few sinusoidal oscillator circuits. A minimum component oscillator circuit, eight grounded passive component sinusoidal oscillator circuits and two sinusoidal oscillator circuits with grounded resistance and capacitance are realized from the generalized configuration.

Quadrature oscillator is an important building block for many electronics and communication applications. Part of this thesis discusses two quadrature sinusoidal oscillator circuits with independent control of condition of oscillation and frequency of oscillation. In addition, two square waveform generators and their advantages with respect to the existing square waveform generators in the literature are presented in detail.

The operation principles and non-idealities of all the proposed circuits are described in detail. All the proposed circuits are designed and developed using Cadence 0.18  $\mu$ m CMOS model parameters. The proposed OTRA based circuits can be operated at  $\pm$  1.8 V supply voltages. The performances of the circuits are explored through Spectre simulation model parameters. The proposed circuits are also designed and checked for waveform generation on a laboratory bread board using IC AD 844 AN.

## TABLE OF CONTENTS

| Title |     | Pag                                                      | e No |

|-------|-----|----------------------------------------------------------|------|

| ACK   | NOV | WLEDGEMENT                                               | i    |

| ABS   | ΓRA | CT                                                       | ii   |

| LIST  | OF  | TABLES                                                   | vii  |

| LIST  | OF  | FIGURES                                                  | viii |

| ABB   | REV | VIATIONS                                                 | xiii |

| СНАР  | TEI | R 1: INTRODUCTION                                        | 1    |

| 1     | .1  | INTRODUCTION TO CURRENT-MODE CIRCUITS                    | 1    |

| 1     | .2  | MOTIVATION OF THE WORK                                   | 3    |

| 1     | 1.3 | THESIS OBJECTIVE                                         | 4    |

| 1     | .4  | ORGANIZATION OF THESIS                                   | 5    |

| СНАР  | TEI | R 2: OPERATIONAL TRANSRESISTANCE AMPLIFIER               |      |

| (OTR  | A)  |                                                          | 8    |

| 2     | .1  | INTRODUCTION                                             | 8    |

| 2     | .2  | CMOS OPERATIONAL TRANSRESISTANCE AMPLIFIER               |      |

|       |     | (OTRA)                                                   | 9    |

|       |     | 2.2.1 Salama OTRA                                        | 9    |

|       |     | 2.2.2 Simulation results                                 | 11   |

|       |     | 2.2.3 OTRA using current differencing buffered amplifier | 13   |

|       |     | 2.2.4 Simulation results                                 | 16   |

| 2     | .3  | OTRA IMPLEMENTATION USING IC AD 844                      | 16   |

| 2     | .4  | SUMMARY                                                  | 18   |

| CHAP  | TEI | R 3: LITERATURE REVIEW                                   | 19   |

| 3     | .1  | INTRODUCTION                                             | 19   |

| 3     | .2  | OTRA APPLICATIONS                                        | 19   |

|       |     | 3.2.1 Differential amplifier using OTRA                  | 19   |

|       |     | 3.2.2 Differential integrator using OTRA                 | 21   |

| 3     | .3  | OTRA BASED SQUARE WAVEFORM GENERATORS                    | 23   |

|       |     | 3.3.1 Simulation results                                 | 2.7  |

|        | 3.3.2 Discussions and conclusions                            |

|--------|--------------------------------------------------------------|

| 3.4    | OTRA BASED SQUARE/TRIANGULAR WAVEFORM                        |

|        | GENERATOR                                                    |

|        | 3.4.1 Simulation results                                     |

|        | 3.4.2 Discussions and conclusions                            |

| 3.5    | OTRA BASED SINUSOIDAL OSCILLATORS                            |

|        | 3.5.1 Simulation results                                     |

|        | 3.5.2 Discussions and conclusions                            |

| 3.6    | SUMMARY                                                      |

| СНАРТЕ | ER 4: NEW OTRA BASED WAVEFORM GENERATORS 4                   |

| 4.1    | INTRODUCTION4                                                |

| 4.2    | SINUSOIDAL OSCILLATORS USING SINGLE OTRA4                    |

|        | 4.2.1 Grounded resistance/capacitance sinusoidal oscillators |

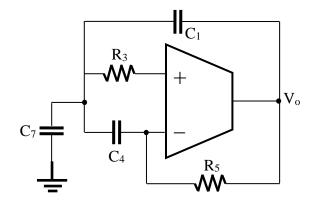

| 4.3    | QUADRATURE SINUSOIDAL OSCILLATORS4                           |

|        | 4.3.1 Proposed quadrature oscillator circuits                |

| 4.4    | SQUARE WAVEFORM GENERATORS 4                                 |

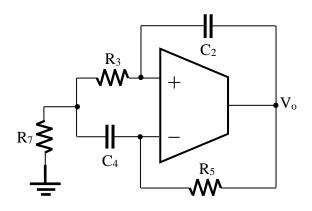

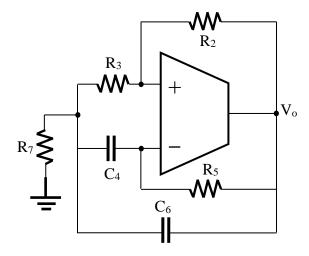

|        | 4.4.1 Proposed square waveform generator circuits 59         |

| 4.5    | SUMMARY5                                                     |

| СНАРТЕ | ER 5: MATHEMATICAL ANALYSIS OF THE PROPOSED                  |

| WAVEF  | ORM GENERATORS5                                              |

| 5.1    | INTRODUCTION                                                 |

| 5.2    | GROUNDED RESISTANCE/CAPACITANCE BASED                        |

|        | SINUSOIDAL OSCILLATOR                                        |

| 5.3    | QUADRATURE SINUSOIDAL OSCILLATORS 5                          |

| 5.4    | SQUARE WAVEFORM GENERATORS 6                                 |

| 5.5    | SUMMARY 6                                                    |

| CHAPTI | ER 6: NON-IDEAL ANALYSIS OF THE PROPOSED                     |

| CIRCUI | TS6                                                          |

| 6.1    | INTRODUCTION                                                 |

| 6.2    | NON-IDEAL MODEL OF THE OTRA                                  |

| 6.3    | NON-IDEAL ANALYSIS OF THE GROUNDED                           |

|        | RESISTANCE/CAPACITANCE BASED SINUSOIDAL                      |

|        | OSCILLATORS6                                                 |

| 6.4    | NON-IDEAL ANALYSIS OF THE PROPOSED         |

|--------|--------------------------------------------|

|        | QUADRATURE SINUSOIDAL OSCILLATORS          |

| 6.5    | NON-IDEAL ANALYSIS OF THE PROPOSED SQUARE  |

|        | WAVEFORM GENERATORS                        |

| 6.6    | SUMMARY                                    |

| CHAPTI | ER 7: SIMULATION RESULTS                   |

| 7.1    | INTRODUCTION                               |

| 7.2    | GROUNDED RESISTANCE/CAPACITANCE SINUSOIDAL |

|        | OSCILLATORS                                |

|        | 7.2.1 Simulation results                   |

| 7.3    | QUADRATURE SINUSOIDAL OSCILLATORS          |

|        | 7.3.1 Simulation results                   |

| 7.4    | SQUARE WAVEFORM GENERATORS                 |

|        | 7.4.1 Simulation results                   |

| 7.5    | SUMMARY                                    |

| CHAPTI | ER 8: HARDWARE IMPLEMENTATION              |

| 8.1    | INTRODUCTION                               |

| 8.2    | GROUNDED RESISTANCE/CAPACITANCE SINUSOIDAL |

|        | OSCILLATORS                                |

|        | 8.2.1 Experimental results                 |

| 8.3    | QUADRATURE SINUSOIDAL OSCILLATORS          |

|        | 8.3.1 Experimental results                 |

| 8.4    | SQUARE WAVEFORM GENERATORS                 |

|        | 8.4.1 Experimental results                 |

| 8.5    | SUMMARY                                    |

| CHAPTI | ER 9: CONCLUSIONS AND SCOPE FOR FUTURE     |

| WORK   |                                            |

| 9.1    | CONCLUSIONS                                |

| 9.2    | SCOPE FOR FUTURE WORK                      |

| DEFEDE | INCES                                      |

## LIST OF TABLES

| <b>Tables</b> | Title Pag                                                           | e No. |

|---------------|---------------------------------------------------------------------|-------|

| Table 4.1     | Selected passive components for the generalized configuration       |       |

|               | shown in 4.2.                                                       | 44    |

| Table 5.1     | Condition of oscillation and frequency of oscillation for the       |       |

|               | proposed circuits in Fig. 4.3 and 4.4                               | 55    |

| Table 6.1     | Non-ideal condition of oscillation and frequency of oscillation for |       |

|               | the proposed circuits in chapter 4                                  | 70    |

| Table 7.1     | Aspect ratios of CMOS OTRA shown in Fig. 7.1                        | 79    |

| Table 8.1     | Comparison of the proposed circuit in Fig. 4.4 (a) with the         |       |

|               | conventional sinusoidal oscillator circuits in the literature       | 105   |

| Table 8.2     | Comparison of the proposed circuit in Fig. 4.7 with the             |       |

|               | conventional square-wave generators in the literature               | 112   |

|               |                                                                     |       |

## LIST OF FIGURES

| Figures   | Title Page                                                             | No. |

|-----------|------------------------------------------------------------------------|-----|

| Fig. 2.1  | OTRA circuit symbol                                                    | 8   |

| Fig. 2.2  | Non-ideal model of OTRA                                                | 10  |

| Fig. 2.3  | CMOS implementation of the Salama OTRA                                 | 10  |

| Fig. 2.4  | Frequency response of the Salama OTRA                                  | 11  |

| Fig. 2.5  | Output voltage at terminal Z in Fig. 2.3                               | 12  |

| Fig. 2.6  | Input resistance plot for the circuit in Fig. 2.3                      | 12  |

| Fig. 2.7  | Output resistance plot for the circuit in Fig. 2.3                     | 13  |

| Fig. 2.8  | Device level implementation of OTRA                                    | 14  |

| Fig. 2.9  | Frequency response of the CMOS circuit shown in Fig. 2.8               | 14  |

| Fig. 2.10 | Output voltage at terminal Z in Fig. 2.8.                              | 15  |

| Fig. 2.11 | Input resistance plot for the circuit shown in Fig. 2.8                | 15  |

| Fig. 2.12 | Output resistance plot for the circuit shown in Fig. 2.8               | 16  |

| Fig. 2.13 | CFOA (AD 844) circuit symbol                                           | 17  |

| Fig. 2.14 | Implementation of OTRA using AD 844 ICs                                | 17  |

| Fig. 3.1  | Differential amplifier using OTRA                                      | 19  |

| Fig. 3.2  | Frequency response of the differential amplifier                       | 20  |

| Fig. 3.3  | Implementation of differential amplifier using MOS-C [41]              | 20  |

| Fig. 3.4  | Differential integrator using OTRA                                     | 22  |

| Fig. 3.5  | Simulated output voltage of the differential integrator                | 22  |

| Fig. 3.6  | Implementation of the OTRA differential integrator using MOS-C [41]    | 22  |

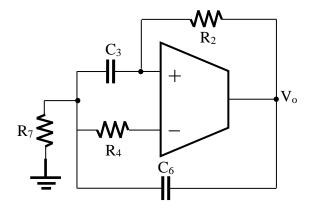

| Fig. 3.7  | OTRA based square waveform generator proposed in [55]                  | 23  |

| Fig. 3.8  | Output waveform of the OTRA based square waveform generator in Fig.    |     |

|           | 3.7                                                                    | 24  |

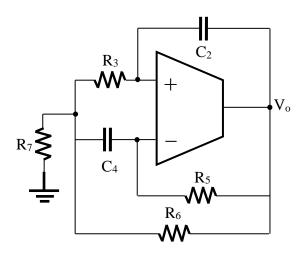

| Fig. 3.9  | Second proposed square waveform generator in [55]                      | 26  |

| Fig. 3.10 | Simulation result of the square waveform generator circuit in Fig. 3.7 | 27  |

| Fig. 3.11 | Simulation result of the square waveform generator circuit in Fig. 3.9 | 28  |

| Fig. 3.12 | Variation of time period for the square waveform generator circuit     |     |

|           | shown in Fig. 3.9                                                      | 29  |

| Fig. 3.13 | OTRA based square/triangle waveform generator                        | 30 |

|-----------|----------------------------------------------------------------------|----|

| Fig. 3.14 | Expected output waveform from the circuit in Fig. 3.13               | 30 |

| Fig. 3.15 | Simulated output waveform from the circuit in Fig. 3.13              | 32 |

| Fig. 3.16 | OTRA based generalized configuration.                                | 33 |

| Fig. 3.17 | Oscillators realized from the generalized configuration in Fig. 3.16 | 33 |

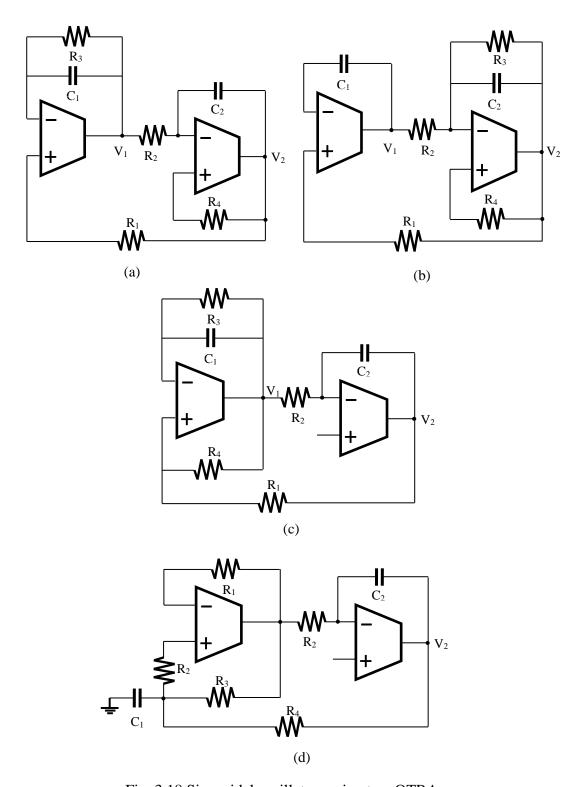

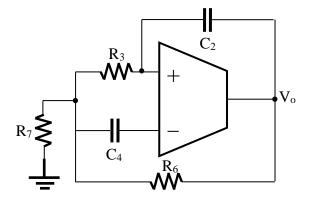

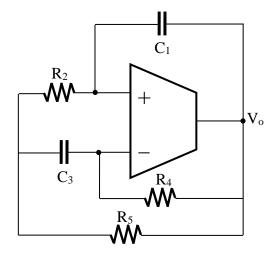

| Fig. 3.18 | Sinusoidal oscillators using two OTRAs                               | 35 |

| Fig. 3.19 | SRCO using single OTRA                                               | 37 |

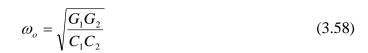

| Fig. 3.20 | Minimum component, SRCO and SCCO oscillators using single OTRA.      | 38 |

| Fig. 3.21 | Simulation result for the oscillator circuit shown in Fig. 3.17 (a)  | 40 |

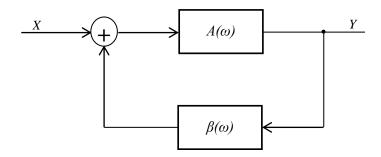

| Fig. 4.1  | Functional block diagram of a sinusoidal oscillator                  | 42 |

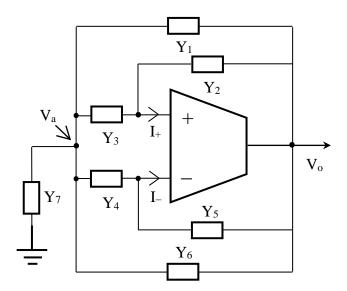

| Fig. 4.2  | Generalized configuration of the Single OTRA based sinusoidal        |    |

|           | oscillators                                                          | 43 |

| Fig. 4.3  | Minimum component RC sinusoidal oscillator                           | 43 |

| Fig. 4.4  | Oscillator circuits realized from the generalized configuration      | 47 |

| Fig. 4.5  | Grounded resistance and capacitance sinusoidal oscillators           | 48 |

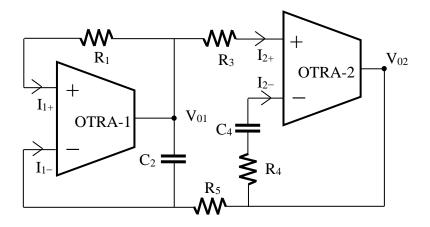

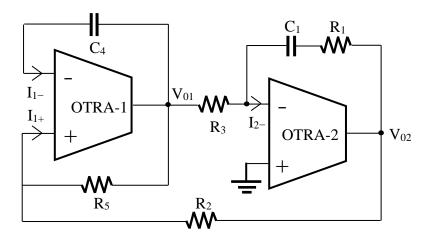

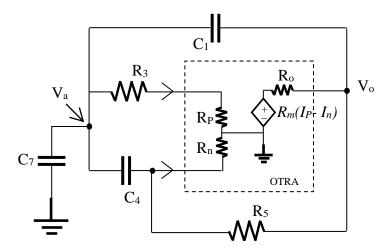

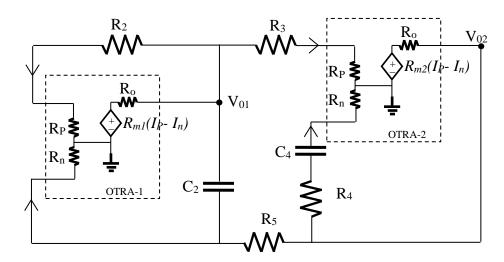

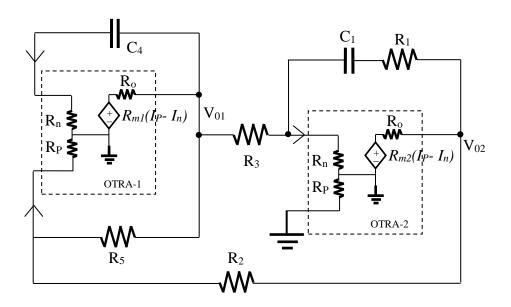

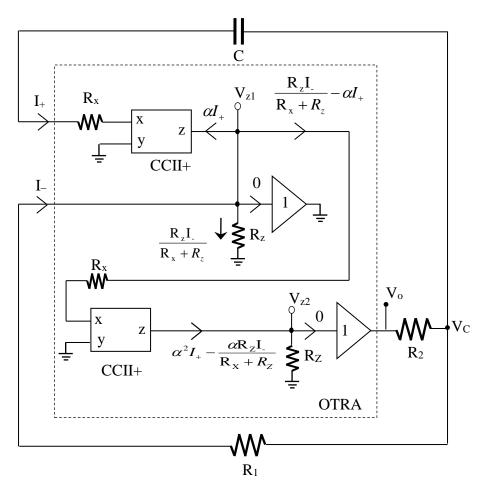

| Fig. 4.6  | Proposed quadrature sinusoidal oscillator circuit-I                  | 49 |

| Fig. 4.7  | Proposed quadrature sinusoidal oscillator circuit-II                 | 49 |

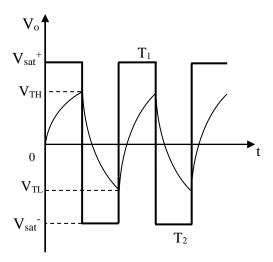

| Fig. 4.8  | Proposed square waveform generator circuits                          | 51 |

| Fig. 4.9  | Expected output waveform of the proposed square-wave generators      | 51 |

| Fig. 5.1  | Generalized configuration of the single OTRA based sinusoidal        |    |

|           | oscillators                                                          | 53 |

| Fig. 5.2  | OTRA based ooscillator circuit realized from Fig. 5.1                | 54 |

| Fig. 5.3  | Grounded resistance and capacitance sinusoidal oscillator circuit-I  | 57 |

| Fig. 5.4  | Grounded resistance and capacitance sinusoidal oscillator circuit-II | 58 |

| Fig. 5.5  | Proposed quadrature sinusoidal oscillator circuit-I                  | 59 |

| Fig. 5.6  | Proposed quadrature sinusoidal oscillator circuit-II                 | 60 |

| Fig. 5.7  | Proposed square waveform generator using OTRA                        | 62 |

| Fig. 5.8  | Output waveform of the proposed circuit shown in Fig. 5.7            | 62 |

| Fig. 5.9  | Second proposed square-wave generator configuration                  | 65 |

| Fig. 6.1  | Equivalent circuit model of the ideal OTRA.                          | 67 |

| Fig. 6.2  | Equivalent circuit model of the non-ideal OTRA                       | 67 |

| Fig. 6.3  | Generalized configuration of the proposed oscillators in chapter 4       | 69 |

|-----------|--------------------------------------------------------------------------|----|

| Fig. 6.4  | Non-ideal OTRA based oscillator circuit                                  | 71 |

| Fig. 6.5  | Non-ideal model of the quadrature sinusoidal oscillator circuit proposed |    |

|           | in chapter 4, Fig. 4.6                                                   | 73 |

| Fig. 6.6  | Non-ideal model of the quadrature sinusoidal oscillator circuit proposed |    |

|           | in chapter 4, Fig. 4.7                                                   | 73 |

| Fig. 6.7  | Non-ideal model of the OTRA implemented with AD 844 ICs                  | 75 |

| Fig. 6.8  | Non-ideal model of the proposed square waveform generator                | 76 |

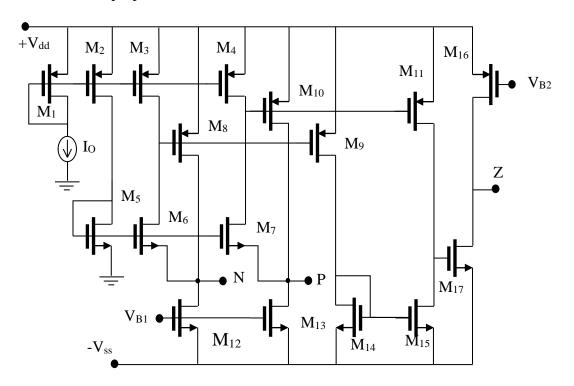

| Fig. 7.1  | CMOS implementation of the OTRA                                          | 78 |

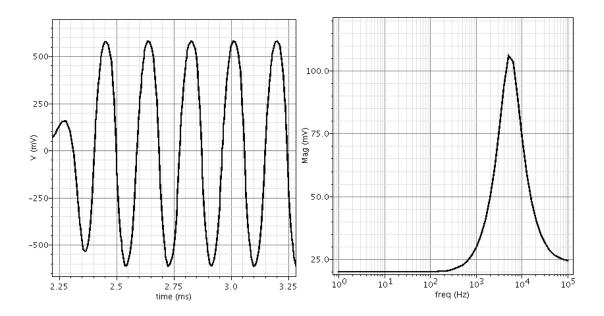

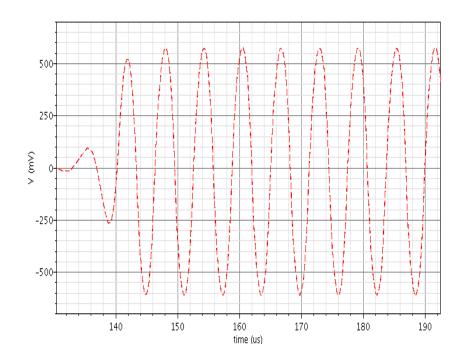

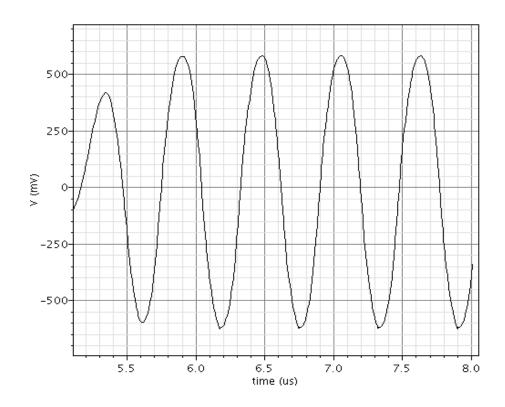

| Fig. 7.2  | Simulated output waveform of the proposed circuit in Fig. 4.3            | 80 |

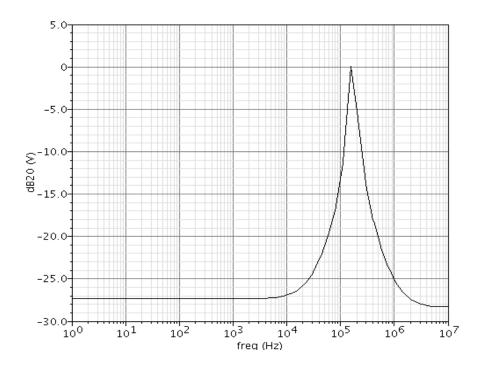

| Fig. 7.3  | Frequency spectrum of the proposed circuit in Fig. 4.3                   | 80 |

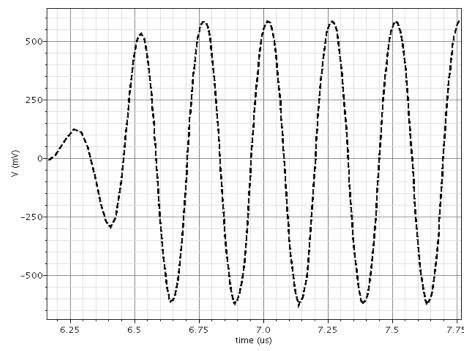

| Fig. 7.4  | Simulated output waveform of the proposed circuit in Fig. 4.4 (a)        | 81 |

| Fig. 7.5  | Simulated output waveform of the proposed circuit in Fig. 4.4 (b)        | 82 |

| Fig. 7.6  | Simulated output waveform of the proposed circuit in Fig. 4.4 (c)        | 82 |

| Fig. 7.7  | Simulated output waveform of the proposed circuit in Fig. 4.4 (d)        | 83 |

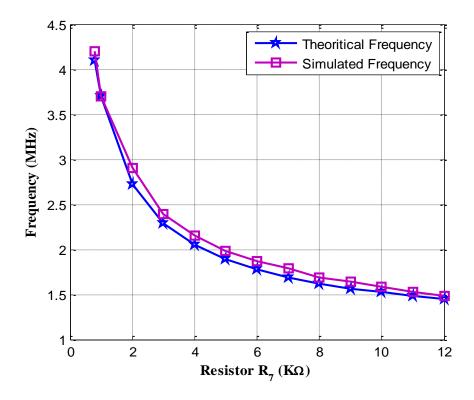

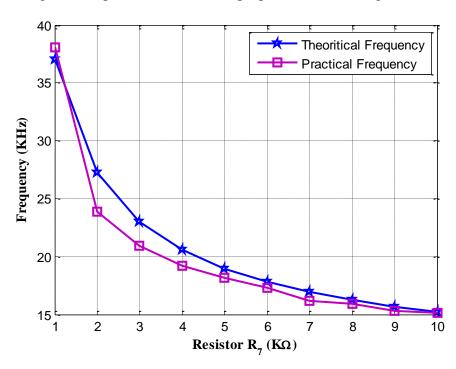

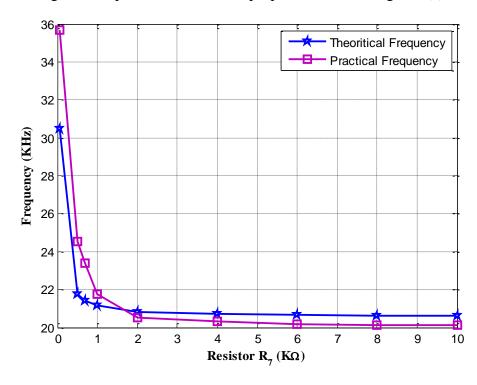

| Fig. 7.8  | Tunability of the proposed circuit in Fig. 4.4 (d) with respect to the   |    |

|           | resistor R <sub>7</sub>                                                  | 83 |

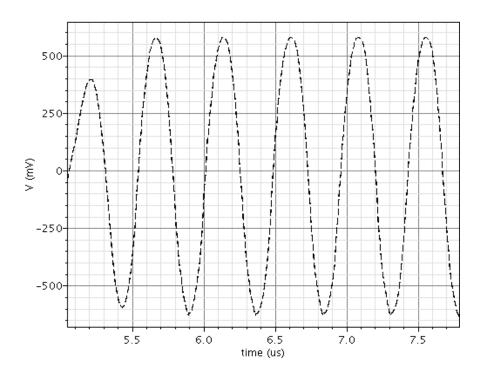

| Fig. 7.9  | Simulated output waveform of the proposed circuit in Fig. 4.4 (e)        | 84 |

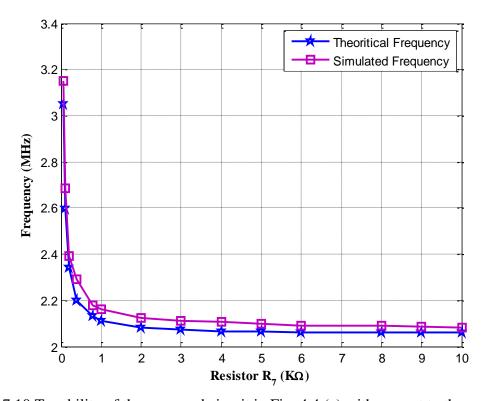

| Fig. 7.10 | Tunability of the proposed circuit in Fig. 4.4 (e) with respect to the   |    |

|           | resistor R <sub>7</sub>                                                  | 84 |

| Fig. 7.11 | Simulated output waveform of the proposed circuit in Fig. 4.4 (f)        | 85 |

| Fig. 7.12 | Simulated output waveform of the proposed circuit in Fig. 4.4 (g)        | 86 |

| Fig. 7.13 | Simulated output waveform of the proposed circuit in Fig. 4.4 (h)        | 86 |

| Fig. 7.14 | Simulated output waveform of the proposed circuit in Fig. 4.4 (i)        | 87 |

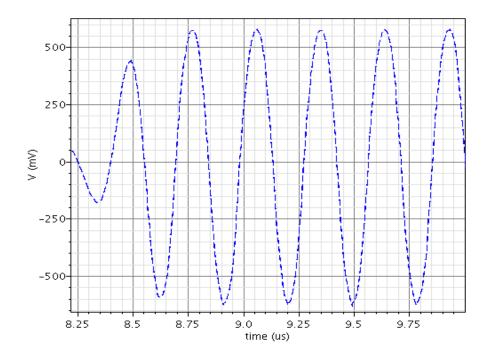

| Fig. 7.15 | Simulated output waveform of the proposed circuit in Fig. 4.5 (a)        | 87 |

| Fig. 7.16 | Frequency spectrum of the proposed circuit in Fig. 4.5 (a)               | 88 |

| Fig. 7.17 | Simulated output waveform of the proposed circuit in Fig. 4.5 (b)        | 88 |

| Fig. 7.18 | Frequency spectrum of the proposed circuit in Fig. 4.5 (b)               | 89 |

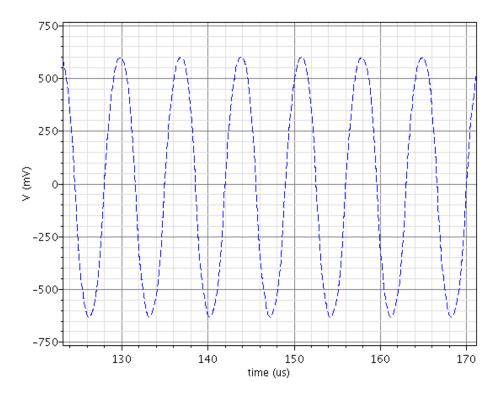

| Fig. 7.19 | Simulated output waveform of the proposed quadrature oscillator circuit  |    |

|           | in Fig. 4.6                                                              | 90 |

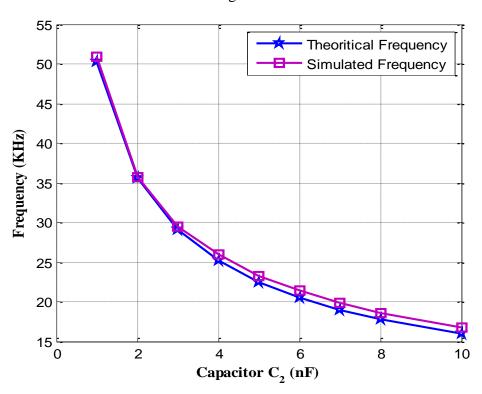

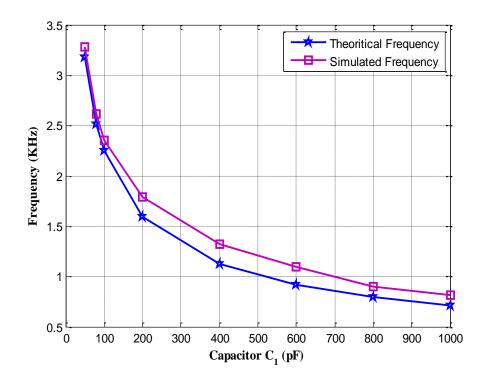

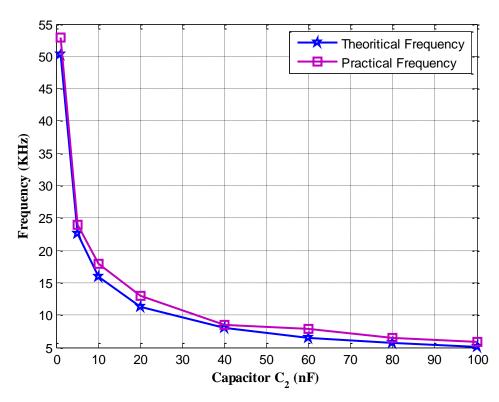

| Fig. 7.20 | Tunability of the proposed circuit in Fig. 4.6 with respect to the       |    |

|           | capacitor C <sub>2</sub>                                                       | 90  |

|-----------|--------------------------------------------------------------------------------|-----|

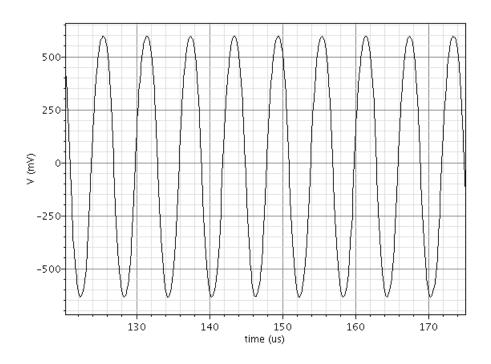

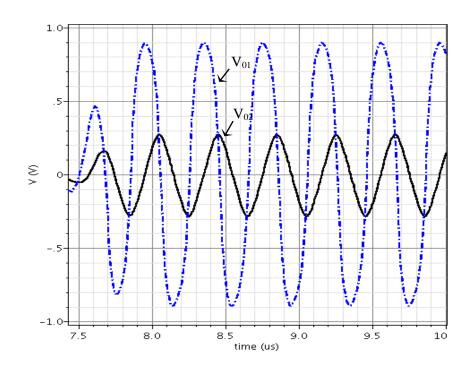

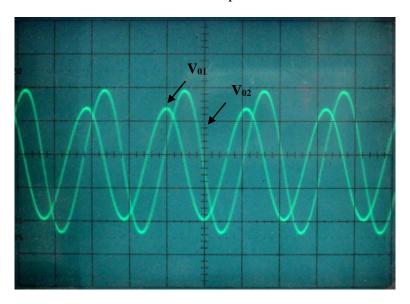

| Fig. 7.21 | Simulated output waveform of the proposed circuit in Fig. 4.7                  | 91  |

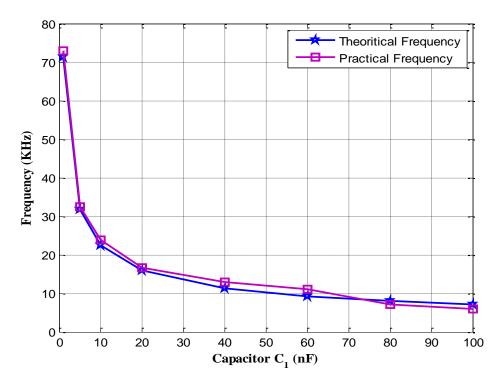

| Fig. 7.22 | Tunability of the proposed circuit in Fig. 4.7 with respect to the             |     |

|           | capacitor C <sub>1</sub>                                                       | 91  |

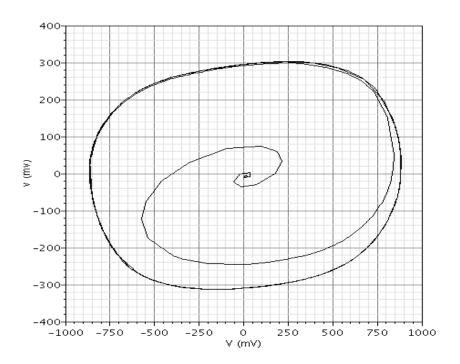

| Fig. 7.23 | Outputs $V_{01} \ Vs \ V_{02}$ of the proposed circuit in Fig. 4.7             | 92  |

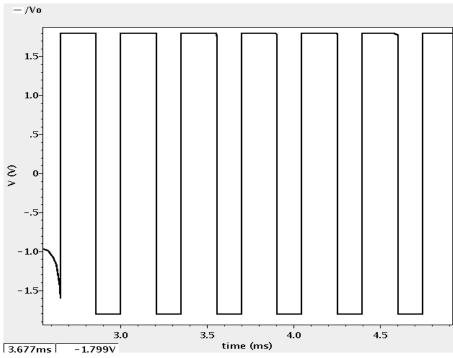

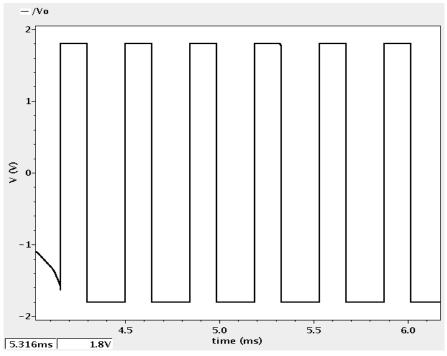

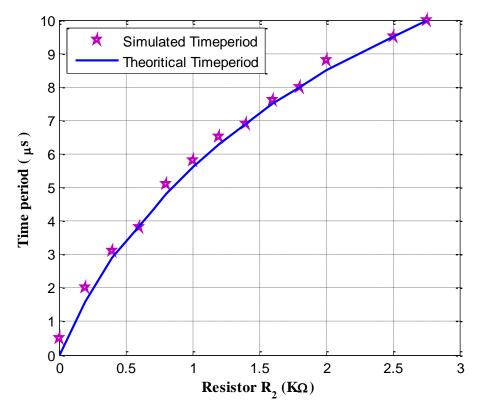

| Fig. 7.24 | Output waveforms of the proposed square-wave generators                        | 94  |

| Fig. 7.25 | Tunability of time period against resistor R <sub>2</sub>                      | 94  |

| Fig. 8.1  | Implementation of OTRA using AD 844 ICs                                        | 97  |

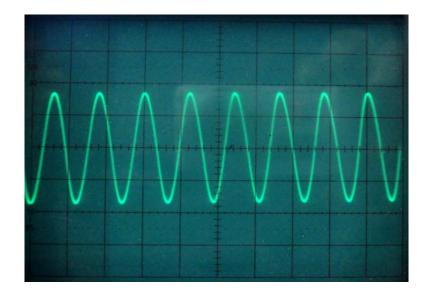

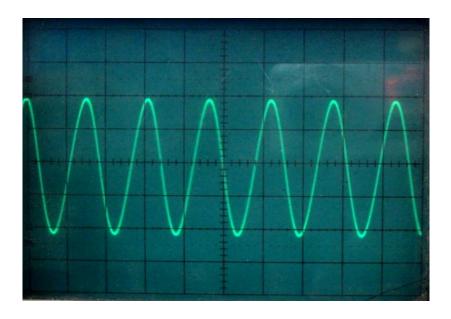

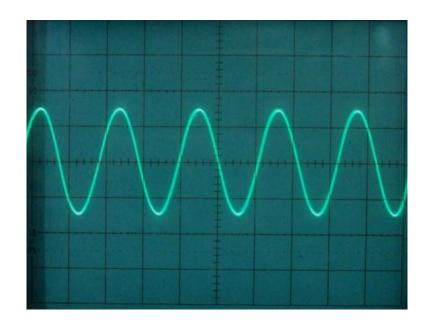

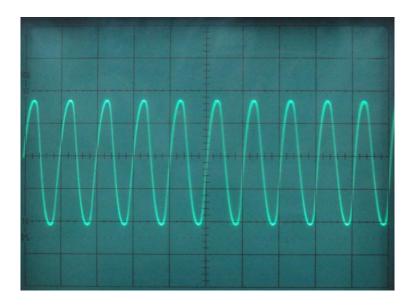

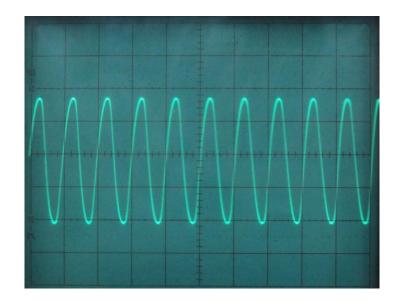

| Fig. 8.2  | Experimental output waveform of the proposed circuit shown in Fig. 4.3         | 97  |

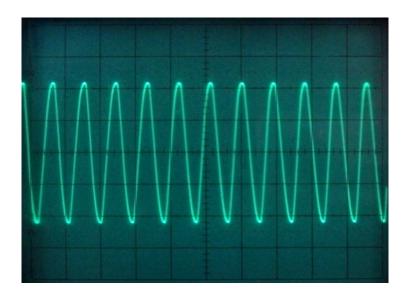

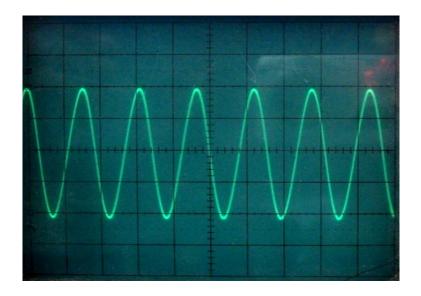

| Fig. 8.3  | Output waveform of the proposed circuit in Fig. 4.4 (a)                        | 98  |

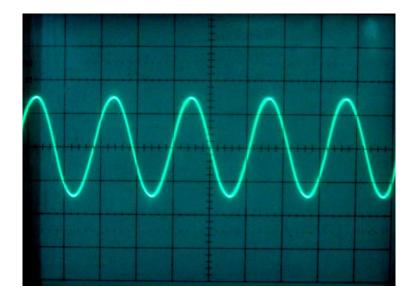

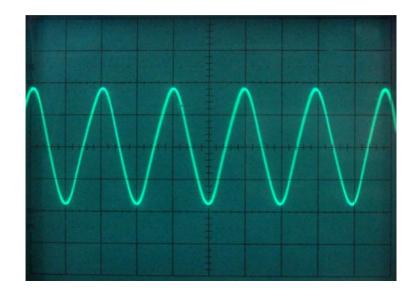

| Fig. 8.4  | Output waveform of the proposed circuit in Fig. 4.4 (b)                        | 98  |

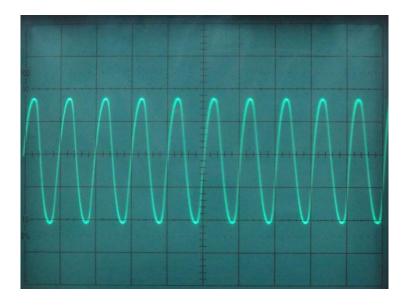

| Fig. 8.5  | Output waveform of the proposed circuit in Fig. 4.4 (c)                        | 99  |

| Fig. 8.6  | Output waveform of the proposed circuit in Fig. 4.4 (d)                        | 100 |

| Fig. 8.7  | Tunability of the proposed circuit in Fig. 4.4 (d) with respect to the         |     |

|           | resistor R <sub>7</sub>                                                        | 100 |

| Fig. 8.8  | Output waveform of the proposed circuit in Fig. 4.4 (e)                        | 101 |

| Fig. 8.9  | Tunability of the proposed circuit in Fig. 4.4 (e) with respect to the         |     |

|           | resistor R <sub>7</sub>                                                        | 101 |

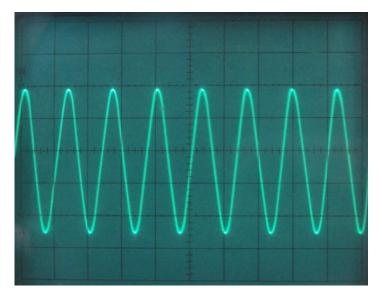

| Fig. 8.10 | Experimental output waveform of the proposed circuit in Fig. 4.4 (f)           | 102 |

| Fig. 8.11 | Experimental output waveform of the proposed circuit in Fig. 4.4 (g)           | 102 |

| Fig. 8.12 | Experimental output waveform of the proposed circuit in Fig. 4.4 (h)           | 103 |

| Fig. 8.13 | Experimental output waveform of the proposed circuit in Fig. 4.4 (i)           | 103 |

| Fig. 8.14 | Experimental output waveform of the proposed circuit in Fig. 4.5 (a)           | 104 |

| Fig. 8.15 | Experimental output waveform of the proposed circuit in Fig. 4.5 (b)           | 104 |

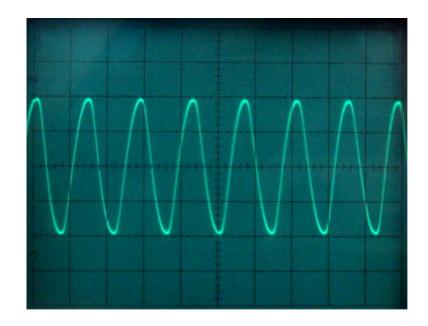

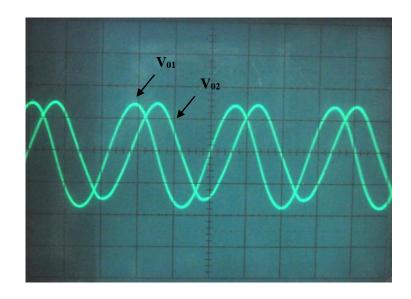

| Fig. 8.16 | Experimental output waveform for the proposed circuit in Fig. 4.6              | 106 |

| Fig. 8.17 | Tunability of the proposed circuit in Fig. 4.6 with respect to the             |     |

|           | capacitor C <sub>2</sub>                                                       | 106 |

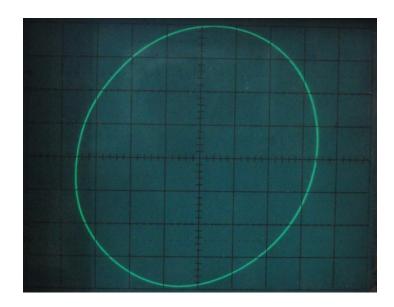

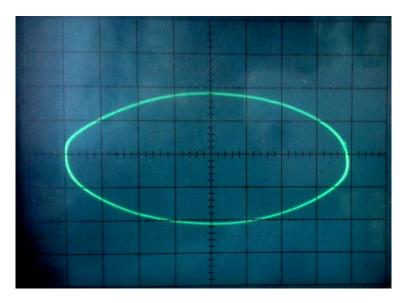

| Fig. 8.18 | The voltages $V_{01}$ versus $V_{02}$ of the proposed quadrature oscillator on |     |

|           | oscilloscope                                                                   | 107 |

| Fig. 8.19 | Experimental output waveform of the proposed circuit in Fig. 4.7               | 107 |

| Fig. 8.20 | Tunability of the proposed circuit in Fig. 4.6 with respect to the             |     |

|      |      | capacitor C <sub>1</sub>                                                       | 108 |

|------|------|--------------------------------------------------------------------------------|-----|

| Fig. | 8.21 | The voltages $V_{01}$ versus $V_{02}$ of the proposed quadrature oscillator on |     |

|      |      | oscilloscope                                                                   | 108 |

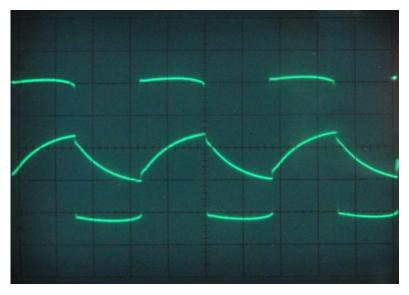

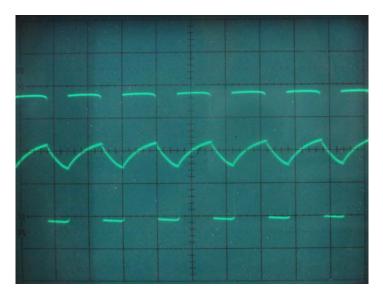

| Fig. | 8.22 | Output waveform with almost equal and fixed duty cycles ( $T_{ON} = T_{OFF}$ ) | 109 |

| Fig. | 8.23 | Experimental output waveforms of the second proposed circuit                   | 110 |

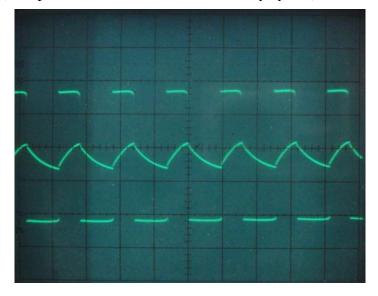

| Fig. | 8.24 | Variation of time period against resistor R <sub>1</sub>                       | 111 |

| Fig. | 8.25 | Tunability against capacitor C                                                 | 111 |

| Fig. | 8.26 | Tunability against resistor R <sub>2</sub>                                     | 113 |

#### **ABBREVIATIONS**

CC Current Conveyor

CC-CDBA Current Controlled Current Differencing Buffered Amplifier

CCCDTA Current Controlled Current Differencing Transconductance Amplifier

CCII Second-Generation Current Conveyor

CDBA Current Differencing Buffered Amplifier

CDTA Current Differencing Transconductance Amplifier

CFOA Current Feed-Back Operational Amplifier

CMOS Complementary Metal Oxide Semiconductor

DCCCS Differential Current Controlled Current Source

DCCII Second Generation Differential Current Conveyor

FTFN Four Terminal Floating Nuller

IC Integrated Circuit

JFET Junction Field Effect Transistor

KCL Kirchhoff's Current Law

MDCC Modified Differential Current Conveyor

MOS-C MOSFET and Capacitors

MOSFET Metal Oxide Semiconductor Field Effect Transistor

OTA Operational Transconductance Amplifier

OTRA Operational Transresistance Amplifier

PID Proportional Integral and Derivative

RF Radio Frequency

VCVS Voltage Controlled Voltage Source

VDTA Voltage Differencing Transconductance Amplifier

VDBA Voltage Differencing Buffered Amplifier

VGA Voltage Gain Amplifiers

VLSI Very Large Scale Integration

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 INTRODUCTION TO CURRENT-MODE CIRCUITS

Sinusoidal/square waveform generators are the basic building cells in many electronic circuit systems. For example, in instrumentation, measurement systems, communication systems, power conversion control circuits and signal processing application [1]. The sinusoidal and square waveform generators along with other circuits are often employed to produce various standard signals, such as triangular wave, pulse wave, etc. Since the introduction of integrated circuits, the operational amplifier (op-amp) has been serving as the basic building block in many electronics circuit designs. Since then, new integrated analogue circuit applications have emerged and the performance requirements for analogue circuits have changed. A typical voltage-mode waveform generator can be implemented by using an op-amp with a few passive components. Verities of waveform generators using voltage mode opamp are available in the literature [2, 3]. These voltage-mode (op-amp) circuits yield some drawbacks such as complex internal circuitries, lower slew rate, constant gain bandwidth product and more passive components are however required to generate the waveforms. The finite gain bandwidth product of an op-amp affects the performance of the waveform generator. Furthermore, the limited slew rate of the opamp affects the large signal and high frequency operations [4-6]. Analogue circuit design has historically been dominated by voltage-mode signal processing. In voltagemode, current signals are transferred into a voltage domain before any analogue signal processing. This makes an integrated circuit (IC) unsuitable for low voltage application. When low voltage, low power consumption and wide bandwidth are required simultaneously, the voltage-mode devices easily become too complex and failed to achieve the required characteristics [7]. The performance of a circuit in analogue circuits is determined in terms of voltage levels at the different nodes in the circuit including input and output nodes are known as voltage mode circuits. Large output voltage swing while minimizing the total power consumption is required to provide in voltage mode circuits. This causes high impedance node architecture in the voltage mode circuits. In voltage mode circuits with large voltage swing, the parasitic capacitances presented in the circuits need to be charged and discharged, this leads to decrease of the speed and slew rate in the voltage mode circuits.

Apart from the op-amps or voltage-mode approaches, another circuit design concept, current-mode technique was introduced [4-7]. The current mode circuits are low impedance circuits. The performance of the current mode circuits in terms of speed and slew rate is very high compared to the voltage mode circuits. By using the current signals instead of voltage signals, the current mode circuits are able to operate with low supply voltages. The addition opeartion in current mode circuit is much easier than the voltage mode circuits. By using KCL (Kirchhoff's Current Law), the addition and subtraction is possible by joining the terminals at a node in the current mode circuit. This eliminates the passive components, reduces the power consumption and chip area compared to the voltage mode. In addition to the above stated advantages, the dynamic range of the current mode circuits is larger than that of the voltage mode circuits. The first current-mode based active device named current conveyor (CC) was introduced in 1968 [6]. Since then, many new active current-mode devices have been reported in the literature [8-17]. Second and third generation current conveyors were introduced in 1970 and 1995 [6]. The terminal relations for the first, second and third generation current conveyors are different. Based on the output terminal current direction, the current conveyors are further classified as CCII+ and CCII-. The Operational Transconductance Amplifier (OTA) is used to drive the capacitive loads [8]. Many applications are available in the literature using Current Feed-back Operational Amplifier (CFOA) [9]. CFOA has the similar terminal relation with respect to the CCII. Few current mode devices are listed below.

- i) Four Terminal Floating Nuller (FTFN)

- ii) Current Differencing Buffered Amplifier (CDBA)

- iii) Current Controlled CDBA (CC-CDBA)

- iv) Current Differencing Transconductance Amplifier (CDTA)

- v) Current Controlled CDTA (CCCDTA)

- vi) Voltage Differencing Transconductance Amplifier (VDTA)

- vii) Voltage Differencing Buffered Amplifier (VDBA)

In previous researches, some waveform generators were presented based on current-mode devices [18-30]. These current-mode waveform generators have attracted much attention of the analogue integrated circuit designers due to the

advantages over voltage mode waveform generators such as; the oscillation frequency can be adjusted more accurately, the oscillation frequency is less sensitive to the bandwidth variation of the active devices and because of the large slew rate, the current-mode oscillator can achieve higher frequencies at larger amplitude levels.

#### 1.2 MOTIVATION OF THE WORK

The modern integrated circuit technologies are normally developed to be driven by the needs of digital CMOS circuit design. As the size of integrated devices decreases, so maximum voltage ratings are also rapidly reduces. Although decreased supply voltages do not restrict the design of digital circuits, it is harder to design high performance analogue integrated circuits using new processes. In digital integration technologies, there are fewer integrated devices available for the circuit design. In the worst case situation, this means that only transistors are available for analogue circuit design. There may occasionally be capacitances and resistors, but their values may be small and there are significant parasitic components present. Thus, if we want to utilize the fastest integration technologies available, which are normally restricted to the active components in the design of integrated analogue circuits. Since the introduction of integrated circuits, the operational amplifier has served as the basic building block in analogue circuit design. When signals are widely distributed as voltages, the parasitic capacitances are charged and discharged with the full voltage swing, which limits the speed and increases the power consumption of voltage-mode circuits.

One procedure for finding alternative, preferably simpler, current-mode approach is preferred rather than the traditional voltage-mode structures for signal processing [4-7]. Current-mode circuits cannot avoid nodes with high voltage swing either, but these are usually local nodes with less parasitic capacitances. Therefore, it is possible to reach higher speed and lower dynamic power consumption with current-mode circuit techniques. Since the concept of the current conveyor was brought into being, there are many current-mode analogue building blocks developed and the related applications have been reported in the literature [8-30].

In the past few years, an active device called Operational Transresistance Amplifier (OTRA) is reported and applied [31-38]. Several OTRA-based implementations have emerged. OTRA, being a current processing analogue building

block, inherits all the advantages of the current mode technique and therefore is ideally suited for high frequency applications [39-43]. It is also free from parasitic input capacitances and resistances as its input terminals are virtually grounded and hence, non-ideality problem is less in circuits implemented with OTRA. Low input, output impedances and device gain which is bandwidth independent are the main advantageous properties of the OTRA. The OTRA has also been using as one of the basic building blocks in the field of analogue signal processing [44-60]. OTRA is designed for low voltage operation, low power consumption, wide bandwidth, high speed, greater linearity and simpler circuit complexity. Several circuits for different applications have been reported in the literature [61-88] based on OTRA as a main active element, such as instrumentation amplifiers, MOSFET-C differentiator, integrators, continuous-time filters, immitance simulators, waveform generators, bistable multivibrators and oscillators.

#### 1.3 OBJECTIVES

In the last decade, few number of current-mode sinusoidal/square waveform generators were introduced in the area of analogue signal processing. However, the researchers still aim to design and develop new waveform generator circuits to improve the characteristics of the existing circuits to achieve better features than their counterparts. These better features can be described as less number of passive components, and less number of active components, high frequency performance/inherent signal bandwidths, greater linearity, lower power consumption, lower supply voltages and simplicity in circuit designing. Sinusoidal/square waveform generators are widely used in analogue signal processing. Few sinusoidal/square waveform circuit realizations using different active building blocks have been reported in the literature. These circuit realizations have some drawbacks such as more active/passive components.

Therefore, the main aim of this thesis is to design, develop and testing of new sinusoidal/square waveform generators. The first intention is to design a generalized configuration for the sinusoidal oscillator with one active component, minimum number of passive components and a grounded resistor/capacitor. By using this generalized configuration a few number of oscillator circuits can be realized. The oscillator circuits, which are realized from the generalized configuration, are

controlled by the single grounded resistance/capacitance. Quadrature oscillator is an important building block in many communication, control systems, instrumentation and measurement systems. Therefore, part of this work is attempted on this issue.

The square-wave generator is widely operated in many electronic fields such as digital, instrumentation and communication systems. Conventional square waveform generator circuits pose some drawbacks such as complex internal circuitries, lower slew rate, constant gain bandwidth product, more passive components and non-linear variation of the time period with respect to the passive components. Hence, the intension is to design a square-wave generator with minimum number of passive components, one active component and improved linearity with respect to the passive components connected to the circuit.

In the first step the theoretical analysis is done. To verify the behaviour of the proposed circuits, OTRA is implemented with CMOS transistors and checked for waveform generation. The feasibility of the proposed circuits is also confirmed by the experimental measurements.

#### 1.4 ORGANIZATION OF THESIS

Chapter (2) deals with an introductory overview of the operational transresistance amplifier (OTRA) and its CMOS implementation. Three CMOS OTRA implementations are discussed in this chapter. These CMOS OTRA implementations are already reported in [32-35]. Two of these CMOS OTRA implementations are based on the modified differential current conveyor (MDCC) and a common source amplifier. The OTRA implemented with differential current controlled current source (DCCCS) followed by a buffer [35] is discussed. The operation of these three OTRAs is studied and simulated using Cadence gpdk 180 nm CMOS model parameters.

Chapter (3) provides the background review of the existed waveform generators by using OTRA. Two square waveform generators, one square/triangle waveform generator and some sinusoidal oscillator circuits existed in the literature [46-58] are discussed in this chapter. These circuits are designed and simulated using Cadence Spectre simulation model parameters. The advantages of these circuits are quoted and their drawbacks have been detected during the implementation and simulation is given in this chapter.

Chapter (4) introduces some new waveform generator circuits. In this chapter, a generalized configuration for sinusoidal oscillator circuits, two quadrature sinusoidal oscillators and two square waveform generator using OTRA are proposed. The generalized configuration proposed in this chapter is used to produce few sinusoidal oscillator circuits. The operations of the proposed circuits to produce oscillations are discussed in detail. The quadrature sinusoidal oscillators and square waveform generators operations are discussed in this chapter.

Chapter (5) describes the mathematical analysis of the proposed circuits in chapter 4. The basic network laws and ideal terminal characteristics of OTRA are applied to the proposed circuits to derive the oscillation frequency and condition of oscillations for the oscillator circuits realized from the generalized configuration. Similarly, the same procedure is applied to derive the mathematical equations for the quadrature sinusoidal oscillators and square waveform generators.

Chapter (6) deals with the non-ideal analysis of the proposed circuits. The transresistance gain of the OTRA is infinite in an ideal case. But, practically, the OTRA transresistance gain is finite and its effect should be considered. In this chapter, all the proposed circuits in chapter (4) are reanalyzed based on non-ideal characteristics of OTRA.

Chapter (7) deals with the simulation results of the proposed circuits in chapter (4). All the proposed circuits are checked for waveform generation by connecting with passive components. The passive component values are calculated from the mathematical equations derived in chapter (5). All the proposed circuits are simulated using Cadence Spectre simulation model parameters. Further the simulation results are presented in this chapter to validate the mathematical analysis carried out in chapter (5).

Chapter (8) presents hardware implementation of the proposed circuits on a laboratory bread board. The OTRA prototype circuit is implemented by using two AD844 AN ICs and external passive components are connected to test the waveform generation of the proposed circuits. The proposed circuits are tuned for different passive component values. Hardware results are given in this chapter to validate the simulation and theoretical analysis.

Chapter (9) presents the advantages of the proposed circuits compared to the existing circuits in the literature based on OTRA. In the end, conclusions and future scope are given in this chapter.

# OPERATIONAL TRANSRESISTANCE AMPLIFIER (OTRA)

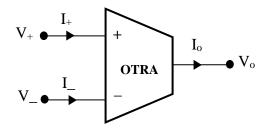

#### 2.1 INTRODUCTION

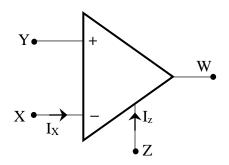

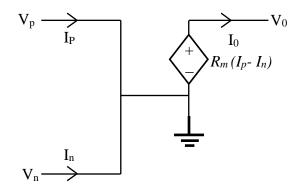

As signal processing extends to higher frequencies, circuit designers are detected, that the traditional design methods based on voltage op-amps are no longer adequate. It is well known that the traditional operational amplifiers have a bandwidth which is dependent on the closed loop voltage gain [1-7]. The attempt to overcome this problem has led to the interest in circuits which operate in current-mode. These circuits employ current processing techniques to improve dynamic speed capability, providing a constant bandwidth virtually independent of the gain. In the last decade, a new current mode device called an operational transresistance amplifier attracted considerable attention of the analogue IC designers. The operational transresistance amplifier is a high gain current input and voltage output analogue building block [31-44]. The circuit symbol of the OTRA is shown in Fig. 2.1. The input and output terminal relations of an OTRA can be characterized by matrix given below Fig. 2.1. For ideal operation, the transresistance gain  $R_m$  approaches infinity forcing the input currents to be equal. Low input and output impedances, a bandwidth independent of the device gain can be considered as the main advantage of the OTRA. Current differencing amplifier and Norton amplifier are the commercially available names of OTRA. These commercial realizations allow input current to flow only in one direction and do not have internal ground at the input terminals. The former disadvantage, limited the functionality of the OTRA, whereas, the latter forced to use external DC bias current leading complex and unattractive designs.

Fig. 2.1 OTRA circuit symbol

$$\begin{bmatrix} V_{+} \\ V_{-} \\ V_{0} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 0 & 0 \\ R_{m} & -R_{m} & 0 \end{bmatrix} \begin{bmatrix} I_{+} \\ I_{-} \\ I_{0} \end{bmatrix}$$

(2.1)

$$V_{+} = V_{-} = 0 (2.2)$$

$$V_o = I_+ R_m - I_- R_m \tag{2.3}$$

In order to overcome these disadvantages of the OTRA, some topologies are proposed in the literature, second generation current conveyor based OTRA implementation is proposed in [32, 35] and [36]. A new norton amplifier based OTRA on current follower configuration with class-AB output stage for low power realization is proposed in [37] and also shows a fully differential implementation to reduce the accurate matching required for current matching. A new CMOS fully differential OTRA design for the low voltage with low power supplies in the submicron technology is reported in [41].

## 2.2 CMOS OPERATIONAL TRANSRESISTANCE AMPLIFIER (OTRA)

#### 2.2.1 SALAMA OTRA

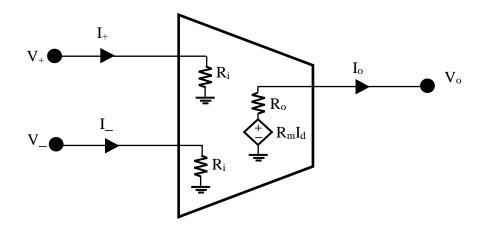

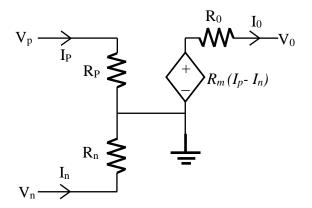

In OTRA both the input and output terminals are characterized by low impedance, thereby eliminating response limitations incurred by capacitive time constants. The input terminals are virtually grounded leading to circuits that are insensitive to stray capacitance. Ideally, the transresistance gain, R<sub>m</sub>, approaches infinity and forces the two input currents I<sub>+</sub> and I<sub>-</sub> to be equal. Practically, the transresistance gain is finite and its effect should be considered along with finite input resistance, output resistance and the frequency limitations associated with the OTRA. Fig. 2.2 shows a simple, non-ideal model of the OTRA with a finite input and output resistance. The input terminals are not virtually grounded, but at a finite voltage determined by the finite input resistance. Also the output voltage is determined by the finite output resistance and the input offset difference current.

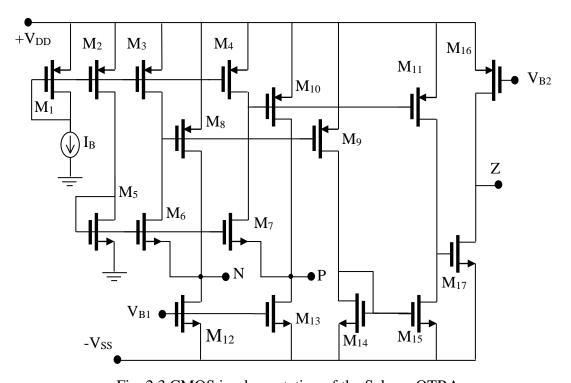

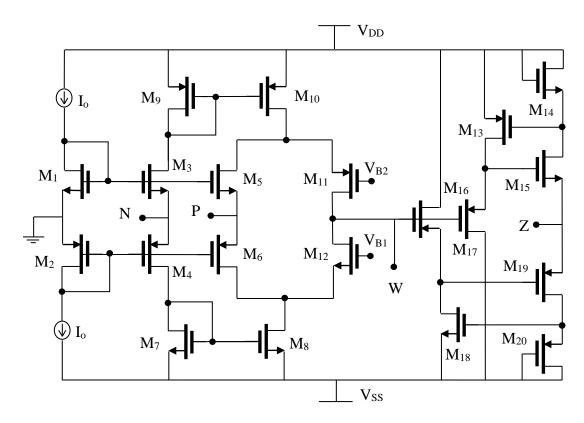

Salama *et al.*, proposed a CMOS OTRA circuit based on the modified differential current conveyor circuit (MDCC) and a common source amplifier [32]. The common source amplifier provides the high gain stage and MDCC provides the current

differencing operation. The CMOS implementing of salama OTRA is shown in Fig. 2.3.

Fig. 2.2 Non-ideal model of OTRA

Fig. 2.3 CMOS implementation of the Salama OTRA

Assuming all the transistors are operating in the saturation region, the circuit operation can be explained as follows. The current mirror formed by  $(M_1-M_4)$  forces equal current  $(I_B)$  in the transistors  $M_5$ ,  $M_6$  and  $M_7$ . This operation derives the gate to source voltages of  $M_5$ ,  $M_6$  and  $M_7$  to be equal and, consequently, forces the two input terminals to be virtually grounded. The current mirrors formed by the transistor pairs  $M_3$  and  $M_4$ ;  $M_8$  and  $M_9$ ;  $M_{10}$  and  $M_{11}$ ;  $M_{14}$  and  $M_{15}$  provide the current differencing

operation, whereas, the common source amplifier formed by  $M_{17}$  achieves the high gain stage. The current biasing  $I_B$ , is connected to the transistors  $M_1$  with common gate and thus biases the transistors  $M_1$  to  $M_4$ . Transistors  $M_3$ ,  $M_6$ ,  $M_8$ ,  $M_9$  and  $M_4$ ,  $M_7$ ,  $M_{10}$ ,  $M_{11}$  form two loops which transmit the current  $I_P$  and  $I_N$  respectively. Hence the output voltage is produced with currents of  $M_9$  and  $M_{11}$ , which biases the output stage transistors in the OTRA design.

#### 2.2.2 SIMULATION RESULTS

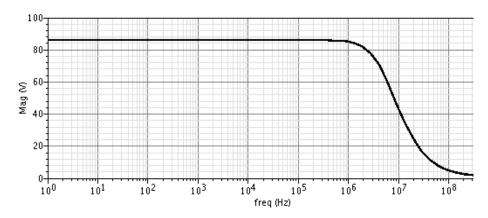

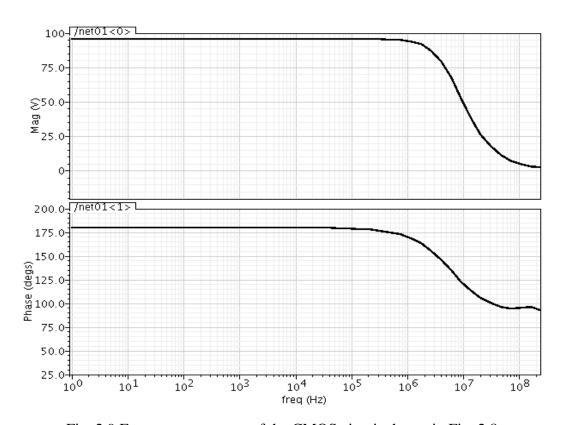

The performance of the Salama OTRA is simulated using Cadence Spectre simulation models and its basic functionality with a central value of specifications at a specific biasing and sizing conditions of the circuit is estimated.

AC Analysis "ac": freq = (1 Hz -> 300 MHz)

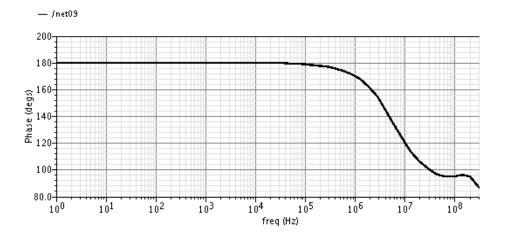

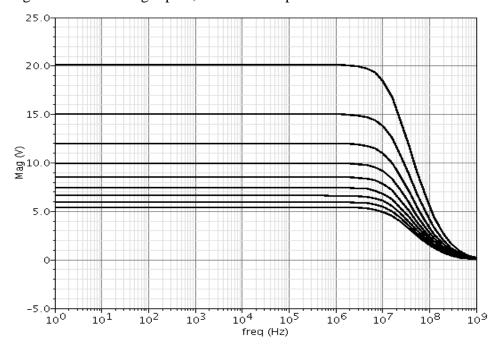

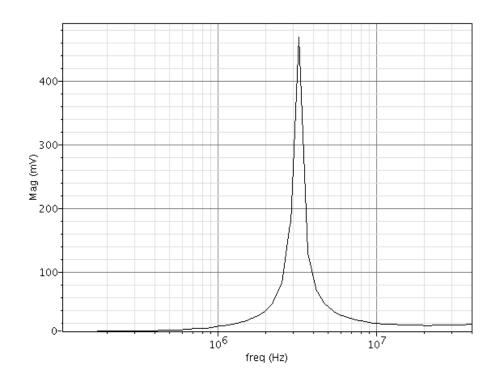

Fig. 2.4 Frequency response of the Salama OTRA

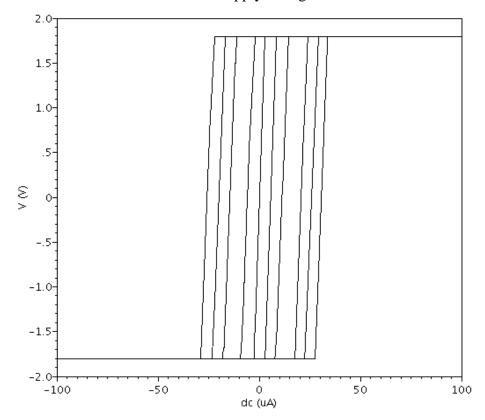

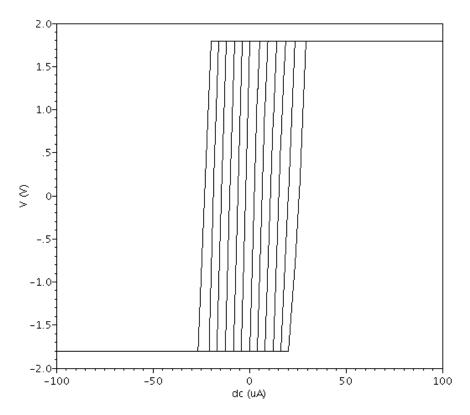

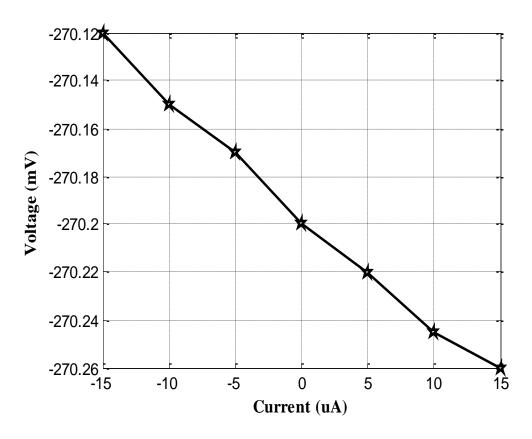

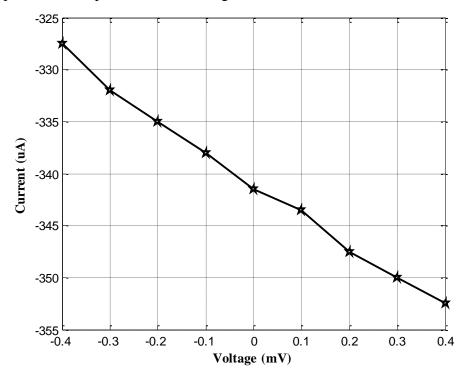

The biasing current  $I_B = 5 \mu A$ , biasing voltages  $V_{B1} = -1 \text{ V}$  and  $V_{B2} = 1.8 \text{ V}$  are used for the simulation of Salama OTRA. Fig. 2.4 shows the magnitude and phase response simulation results of the Salma OTRA. From this AC characteristic, the open loop transresistance gain of the OTRA is  $80.1 \text{ dB}\Omega$  and the transresistance gain bandwidth is 11.3 MHz. Fig. 2.5 shows the output voltage of the OTRA for different

values of inverting input and non-inverting input currents. From this plot, the input current differential range is from -30  $\mu$ A to +30  $\mu$ A. The input resistance plot for the Salama OTRA is shown in Fig. 2.6 and the output resistance plot is shown in Fig. 2.7. The Salama OTRA is simulated with a supply voltage of  $\pm$  1. 8 V.

Fig. 2.5 Output voltage at terminal Z in Fig. 2.3

Fig. 2.6 Input resistance plot for the circuit in Fig. 2.3

Fig. 2.7 Output resistance plot for the circuit in Fig. 2.3

## 2.2.3 OTRA USING A CURRENT DIFFERENCING BUFFERED AMPLIFIER

Ali Toker et al., proposed a new CMOS implementation for current differencing buffered amplifier (CDBA) in [33]. The CDBA can easily be implemented by CMOS transistors by using the configuration shown in Fig. 2.8. This CDBA CMOS implementation can also be used as OTRA and current feedback operational amplifier (CFOA). This CMOS implementation consists of a differential current controlled current source (DCCCS) followed by a voltage buffer. Assuming all the transistors are in the saturation region, the circuit operation is explained as follows. The current mirrors formed by the transistors M<sub>1</sub>, M<sub>3</sub> and M<sub>5</sub> forces equal currents in the transistors M<sub>9</sub> and M<sub>10</sub>. The current mirrors M<sub>2</sub>, M<sub>4</sub> and M<sub>6</sub> forces equal current in the transistors M<sub>7</sub> and M<sub>8</sub>. M<sub>1</sub> and M<sub>2</sub> transistors sources are connected to ground. This operation makes the gate to source voltages of the transistors M<sub>1</sub>-M<sub>6</sub> to be equal and consequently, forces the two input terminals to be virtually grounded. The current mirror transistors from  $M_1$  to  $M_{10}$  and transistors  $M_{11}$  and  $M_{12}$  provides current differencing operation, whereas, the rest of the circuit provides a high gain stage. The bias currents I<sub>0</sub> are given to biases the transistors M<sub>1</sub>-M<sub>6</sub>. By removing the output terminal W in the CMOS implementation shown in Fig. 2.8, it will be converted as OTRA. The transistor M<sub>5</sub> and M<sub>6</sub> can be removed to form a CFOA.

Fig. 2.8 Device level implementation of OTRA

Fig. 2.9 Frequency response of the CMOS circuit shown in Fig. 2.8

Fig. 2.10 Output voltage at terminal Z in Fig. 2.8

Fig. 2.11 Input resistance plot for the circuit shown in Fig. 2.8

#### 2.2.4 SIMULATION RESULTS

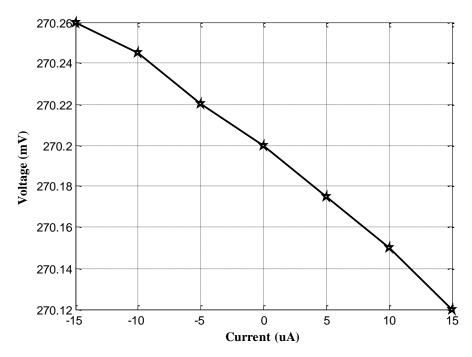

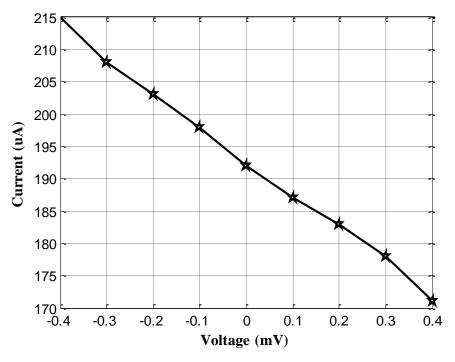

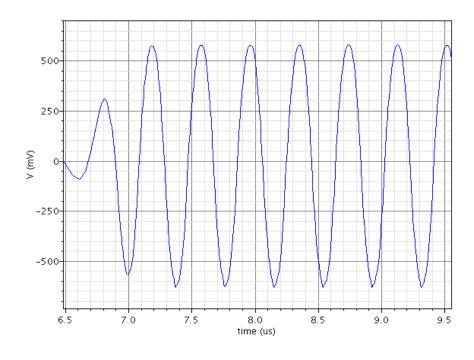

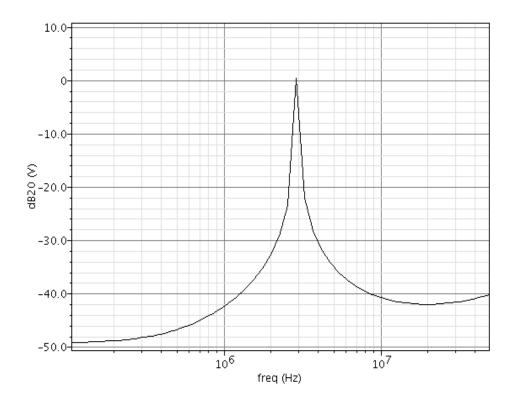

The functionality of the CMOS OTRA shown in Fig. 2.8 is simulated by using Cadence Spectre simulation models. The biasing current  $I_0 = 20~\mu A$ , biasing voltage  $V_{g1} = 0.8~V$  and  $V_{g2} = -0.8~V$  with a supply voltage of  $\pm 1.8~V$  is applied to the CMOS circuit shown in Fig. 2.8. The magnitude and phase response simulation results of the OTRA depicted in Fig. 2.8 is shown in Fig. 2.9. From this AC characteristic, the open loop transresistance gain of the OTRA is 93.31 dB $\Omega$  and the transresistance gain bandwidth is 5.3 MHz. The output voltage of the OTRA for different values of inverting input and non-inverting input currents is shown in Fig. 2.10. The input and output resistance plots are sown in Fig. 2.11 and 2.12.

Fig. 2.12 Output resistance plot for the circuit shown in Fig. 2.8

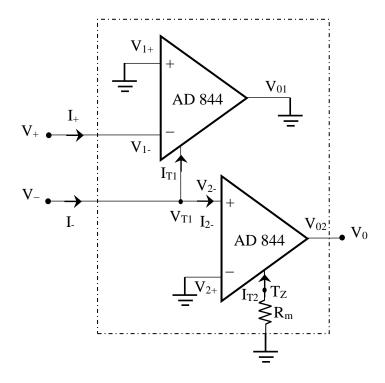

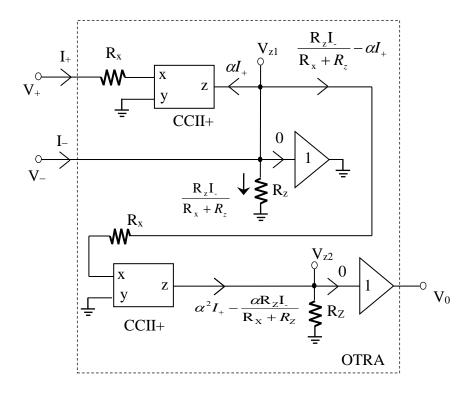

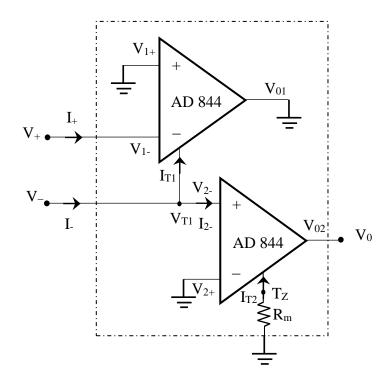

#### 2.3 OTRA IMPLEMENTATION USING IC AD 844

The operational transresistance amplifier can also be implemented using the commercially available IC called a current feedback operational amplifier (CFOA) AD 844 AN [46-49]. The CFOA is a three terminal active device. The circuit symbol of the CFOA is shown in Fig. 2.13. The OTRA implementation using the IC AD 844 AN is shown in Fig. 2.14. Two AD 844 AN ICs and a resistor are used to construct the OTRA. The non-inverting terminals of the AD 844 ANs have been grounded, to

simulate the virtual ground, for the terminals of the OTRA. The following equations can be obtained from the Fig. 2.14.

Fig. 2.13 CFOA (AD 844) circuit symbol

Fig. 2.14 Implementation of OTRA using AD 844 ICs

$$\begin{bmatrix} I_{Y} \\ V_{X} \\ I_{Z} \\ V_{W} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} V_{Y} \\ I_{X} \\ V_{Z} \\ I_{W} \end{bmatrix}$$

(2.4)

$$V_{+} = V_{1-} = V_{1+} = 0 (2.5)$$

$$V_{-} = V_{2-} = V_{2+} = 0 (2.6)$$

$$V_{01} = V_{T1} = V_{2-} = V_{2+} = 0 (2.7)$$

$$I_{T1} = I_{1-} = I_{+} \tag{2.8}$$

$$I_{T2} = I_{2-} = I_{-} - I_{T1} = I_{-} - I_{+}$$

(2.9)

$$V_0 = V_{T2} = -R_m \times I_{T2} = R_m (I_+ - I_-)$$

(2.10)

Therefore, the behavior of the OTRA is obtained with the schematic shown in Fig. 2.14. In this figure, if the  $T_Z$  node of the second AD 844 AN is open circuited then the transresistance gain  $R_m$  is infinite ( $R_m = \infty$ ). With the schematic shown in Fig. 2.14, the proposed circuits in chapter 4 can be implemented on laboratory bread board to check the theoretical analysis.

#### 2.4 SUMMARY

In this chapter, the OTRA characteristics are given in detail. The ideal OTRA based terminal relations are presented along with the OTRA non-ideal model. The CMOS OTRA realizations proposed in [32, 33] are redesigned using cadence gpdk 180 nm technology. Spectre simulation models are used to simulate the CMOS OTRAs. Two CMOS OTRA realizations are presented in this chapter. The simulation results of input terminal resistance, output terminal resistance and the frequency response of the OTRA are included in this chapter. The OTRA prototype model is also presented in this chapter using two AD 844 AN ICs. This prototype model is helpful in the performance evaluation of OTRA based circuits on a laboratory breadboard.

#### CHAPTER 3

### LITERATURE REVIEW

#### 3.1 INTRODUCTION

Having now established some background about the operational transresistance amplifier, let us turn our attention to discuss some applications of OTRA. OTRA is one of the most important building block in the field of analogue integrated circuit. It can be used to realize different applications such as: differential integrator, differential amplifier, voltage gain amplifiers (VGAs), filters, proportional integral and derivative (PID) controllers, analogue multiplier, immitance simulators, oscillators and square/triangular waveform generator [45-89]. The input terminals of the OTRA are virtually grounded, in consequence, most of the parasitic capacitances and resistances will be disappeared. Then it is possible to obtain accurate transfer function by using OTRA in a negative feedback loop. By using OTRA, it is possible to design the applications without linear passive resistances and it is a known fact, the resistance occupies the large silicon area. The OTRA based applications like filters, differential integrator, differential amplifier and VGAs are implemented without using the passive linear resistors.

#### 3.2 OTRA APPLICATIONS

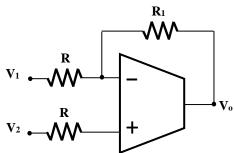

#### 3.2.1 DIFFERENTIAL AMPLIFIER USING OTRA

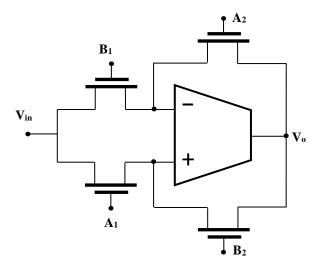

The differential amplifier using OTRA [31] with three resistors is shown in Fig. 3.1. This differential amplifier is also called as voltage controlled voltage source (VCVS).

Fig. 3.1 Differential amplifier using OTRA

The output voltage of the differential amplifier circuit shown in Fig. 3.1 is given by

$$V_0 = K(V_2 - V_1) (3.1)$$

where

$$K = \frac{R_1}{R}$$

The circuit in Fig. 3.1 has the advantage of providing equal gain for both inverting and non-inverting inputs, which is independent of bandwidth.

Fig. 3.2 Frequency response of the differential amplifier

Fig. 3.3 Implementation of differential amplifier using MOS-C [31]

This property is unavailable in traditional voltage-mode (op-amp) devices. The Fig. 3.2 shows the simulation results of the circuit depicted in Fig. 3.1. The passive component values used for the simulation are  $R_1$  is kept constant and R is varied from  $1 \text{ k}\Omega$  to  $10 \text{ k}\Omega$ . The circuit in Fig. 3.1 can also be implemented without using the resistors. The circuit shown in Fig. 3.3 was introduced in [31]. In this work, the application of the OTRA is implemented using MOS-resistors with the non-linearity cancellation technique. The controlled voltage applied to the gate terminal of the transistors can be used to control the conductance G. This implementation is also called as MOS-C (MOSFET and capacitors) implementation. The output voltage at  $V_0$  terminal is given by:

$$V_{o} = (G_{1}/G_{2})V_{i} \tag{3.2}$$

where

$$G_{1} = K_{N1}(V_{A1} - V_{B1}) (3.3)$$

and

$$G_2 = K_{N2}(V_{A2} - V_{B2}) (3.4)$$

$$K_N = \mu C_{OX} \left( \frac{W}{L} \right) \tag{3.5}$$

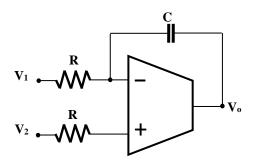

#### 3.2.2 DIFFERENTIAL INTEGRATOR USING OTRA

The differential integrator circuit is shown in Fig. 3.4 with two resistors and a negative feedback capacitor [31]. The effect of stray capacitance is reduced by the virtual grounded connection of the feedback capacitor. The advantage of the proposed circuit is, it is possible to get both the positive and negative transfer function. The output voltage at terminal  $V_{\rm o}$  can be given as

$$V_o = \frac{\omega_o}{s} (V_2 - V_1) \tag{3.6}$$

where

$$\omega_o = \frac{1}{RC}$$

(3.7)

Fig. 3.4 Differential integrator using OTRA

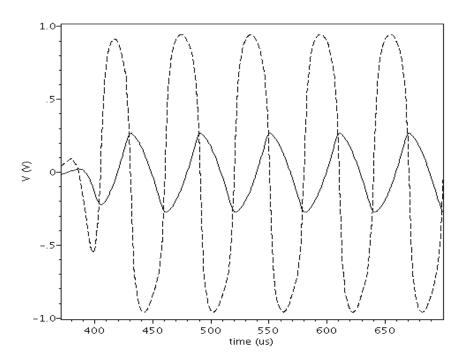

Fig. 3.5 Simulated output voltage of the differential integrator

Fig. 3.6 Implementation of the OTRA differential integrator using MOS-C [31]

The transient response of the circuit in Fig. 3.4 is shown in Fig. 3.5. A feedback resistor is connected in parallel with the capacitor to solve the infinite gain problem in differential integrator circuit in Fig. 3.4. The advantage of connecting the capacitor in the feedback loop is to achieve the self compensation without any additional elements. The MOS-C implementation of the differential integrator using OTRA is shown in Fig. 3.6. The transfer function of the circuit in Fig. 3.6 is given by

$$\frac{V_o}{V_i} = \frac{G_1}{G_2} \frac{1}{\frac{s}{\omega_o} + 1}$$

(3.8)

Where

$$\omega_o = \frac{G_2}{C} \tag{3.9}$$

By adjusting the values of the gate voltages the differential integrator can achieve both ideal and lossy integration. The ideal integration can be done by making  $V_{A2}$  and  $V_{B2}=0$ .

#### 3.3 OTRA BASED SQUARE WAVEFORM GENERATORS

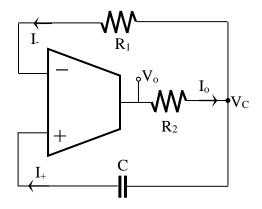

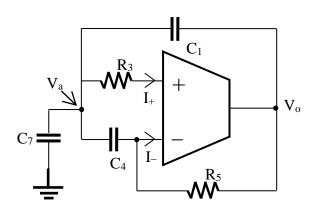

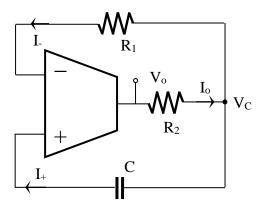

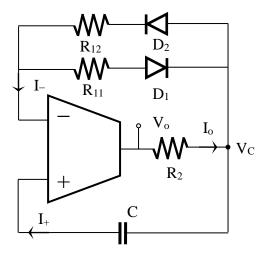

The first OTRA based square waveform generator was proposed by C. L. Hou *et al.*, [45] in the year 2005. In this work [45], two square waveform generators were proposed, these circuits consists of only one OTRA and a few external passive components.

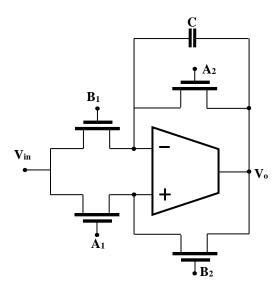

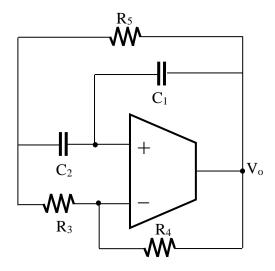

Fig. 3.7 OTRA based square waveform generator proposed in [45]

The first circuit was built with one OTRA and three passive components to produce the symmetrical square waveform with approximately fixed duty cycles and a variable frequency. The second circuit is able to control the on-duty and off-duty cycles of a square waveform independently by varying the value of the passive elements. This circuit was built with one OTRA, two diodes along with a few passive components. The first circuit with one OTRA and three passive components is shown in Fig. 3.7. The square waveform generators in [45] are simpler than the traditional voltage mode based (op-amp) waveform generators.

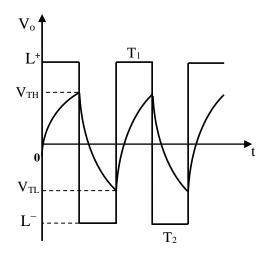

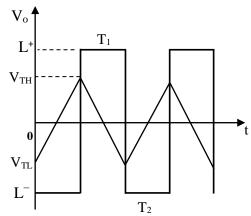

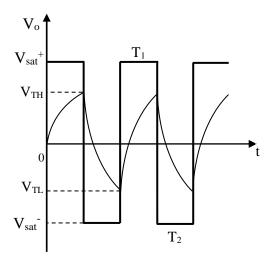

Fig. 3.8 Output waveform of the OTRA based square waveform generator in Fig. 3.7

The operation of the square waveform generator circuit in Fig. 3.7 can be explained with the help of its output waveform shown in Fig. 3.8. The output waveform in Fig. 3.8 has two saturation levels  $L^+$  and  $L^-$ . Initially the output voltage  $V_0$  is at any one of these two saturation levels. The operation of the circuit can be explained as follows. Assume  $V_0$  is changing its state from  $L^-$  to  $L^+$  at the time t=0. At this time, the voltage  $V_C$  of the capacitor C starts to increase from its lower threshold value  $V_{TL}$  to its final value  $L^+$ . Where  $V_{TL}$  is the initial capacitor voltage at t=0. In consequence, the capacitor voltage is finally charged to its upper threshold value  $V_{TH}$ , rather than  $L^+$ . When  $t=T_1$ , it also indicates that the current flowing into the non-inverting input terminal  $I_+$  becomes slightly less than the inverting input terminal  $I_-$  current. So the output changes its state to the lower saturation level  $L^-$ . The upper threshold value and lower threshold value are derived from the non-inverting input terminal current  $I_+$ , inverting input terminal current  $I_-$  and from the ideal behaviour of OTRA is given in equations (3.10) and (3.11).

$$V_{TL} = \left(1 - \frac{R_2}{R_1}\right) L^{-} \tag{3.10}$$

$$V_{TH} = \left(1 - \frac{R_2}{R_1}\right) L^+ \tag{3.11}$$

Then the time period  $T_1$  in Fig. 3.8 can be expressed as

$$T_{1} = R_{2}C \ln \left( \frac{V_{TL} - L^{+}}{V_{TH} - L^{+}} \right)$$

(3.12)

$$R_2 C \ln \left( \frac{2R_1}{R_2} - 1 \right) = T_{on} \tag{3.13}$$

For time period  $T_2$ , the  $V_0$  remains at  $L^-$  and capacitor discharged until the non-inverting input terminal current  $I_+$  becomes larger than inverting input terminal current  $I_-$ , when  $V_C = V_{TL}$ . The dynamic equation of  $V_C$  in the time period  $T_2$  can be expressed as

$$T_2 - T_1 = R_2 C \ln \left( \frac{V_{TH} - L^{-}}{V_{TL} - L^{-}} \right)$$

(3.14)

$$R_2 C \ln \left( \frac{2R_1}{R_2} - 1 \right) = T_{off}$$

(3.15)

From equations (3.14) and (3.15), for producing a square waveform in the circuit shown in Fig. 3.7, it is necessary that

$$R_1 > R_2$$

(3.22)

The output square wave frequency  $f_o$  at the output terminal of the OTRA is given as

$$f_0 = \frac{1}{2R_2C\ln\left(\frac{2R_1}{R_2} - 1\right)}$$

(3.23)

The on-duty and off-duty cycles of the square waveform for the Fig. 3.7 are almost fixed and it is not possible to increase or decrease the width of the duty cycles.

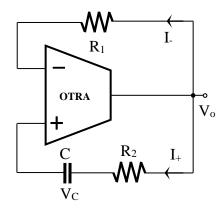

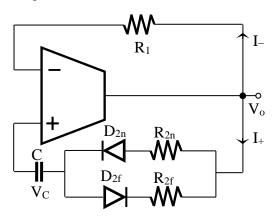

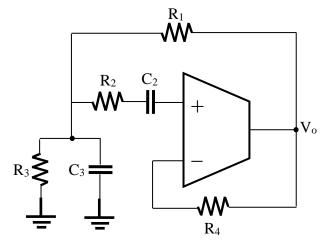

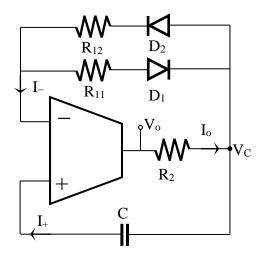

To eliminate this disadvantage, the second circuit was proposed in [45]. This circuit was designed with one OTRA, two diodes and four passive components. The second circuit is shown in Fig. 3.9.

Fig. 3.9 Second proposed square waveform generator in [45]

The operation of the second proposed circuit in Fig. 3.9 is same as stated in the first proposed circuit operation. Neglecting the voltage drops of the diodes in the Fig. 3.9, the equations for the square waveform generator can be expressed as

$$T_{on} = R_2 C \ln \left( \frac{V_{TL} - L^+}{V_{TH} - L^+} \right)$$

(3.26)

$$R_{2n}C\ln\left(\frac{2R_1 - R_{2f}}{R_{2n}}\right) = T_{on}$$

(3.27)

$$T_{off} = R_{2f} C \ln \left( \frac{V_{TH} - L^{-}}{V_{TL} - L^{-}} \right)$$

(3.28)

$$R_{2f}C\ln\left(\frac{2R_1 - R_{2n}}{R_{2f}}\right) = T_{off}$$

(3.29)

$$f_o = \frac{1}{C \left( R_{2n} \ln \left( \frac{2R_1 - R_{2f}}{R_{2n}} \right) + R_{2f} \ln \left( \frac{2R_1 - R_{2n}}{R_{2f}} \right) \right)}$$

(3.30)

To produce a square waveform in the second proposed circuit, it is necessary to maintain

$$R_1 > R_{2n}$$

(3.31)

and

$$R_1 > R_{2f}$$

(3.32)

The on-duty  $(T_{on})$  and off-duty  $(T_{off})$  cycles can be varied independently by adjusting  $R_{2n}$  and  $R_{2f}$  respectively.

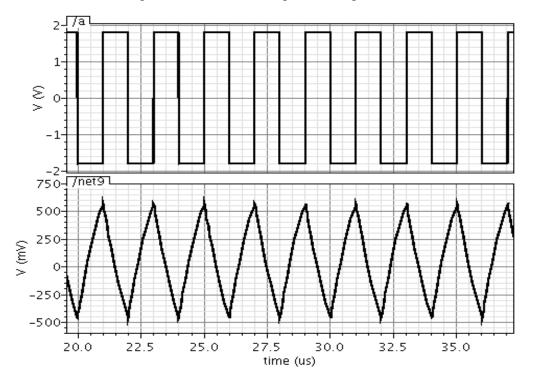

#### 3.3.1 SIMULATION RESULTS

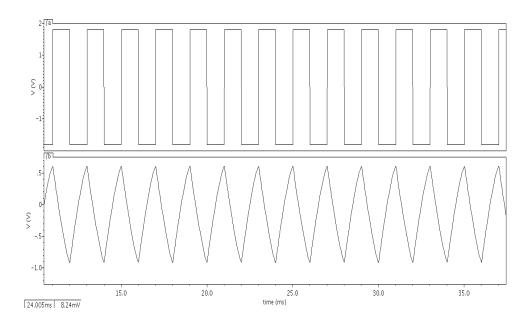

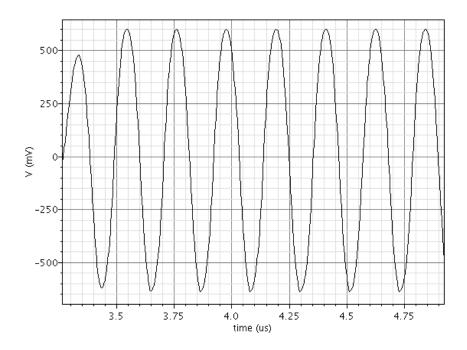

For designing the fixed duty cycle circuit shown in Fig. 3.7, the operating frequency  $f_o$  is chosen first. Then the value of resistors  $R_1$  and  $R_2$  is chosen. The ratio of  $R_1/R_2$  is chosen as low as possible. The larger  $R_1/R_2$  ratio results in a less sensitivity of the frequency variation with respect to the resistance. The capacitor value is arbitrarily chosen from the equation (3.23).

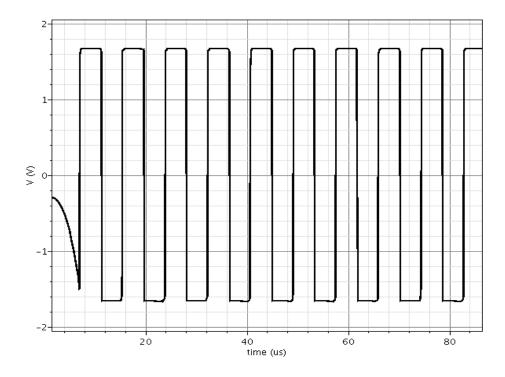

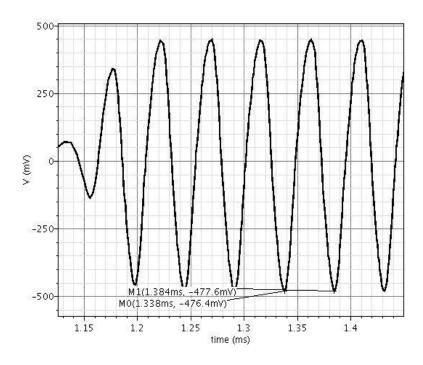

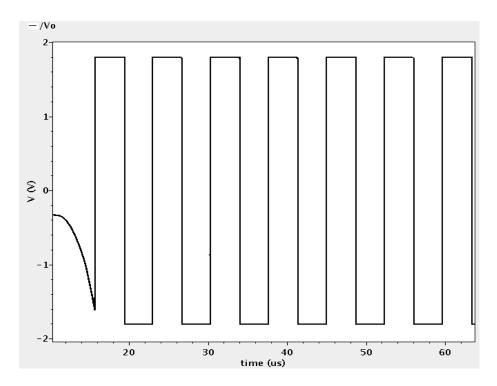

Fig. 3.10 Simulation result of the square waveform generator circuit in Fig. 3.7

For example, if  $f_o$  is chosen as 100 kHz, then the ratio of resistors  $R_1/R_2$  is set to be 10 and C is arbitrarily chosen as 1nF. Then  $R_2$  and  $R_1$  can be calculated from equation (3.23) as 1.7 k $\Omega$  and 17 k $\Omega$ . If the required frequency is 100 Hz, then 1 nF capacitor is replaced by 1  $\mu$ F capacitor without changing the  $R_1/R_2$  ratio. In order to investigate the circuits proposed in [45], several experiments were performed on circuits shown in Fig. 3.7 and Fig. 3.9 at supply voltages  $\pm$  1.8 V. The Cadence Spectre simulation result for the proposed circuit in Fig. 3.7 is shown in Fig. 3.10 with

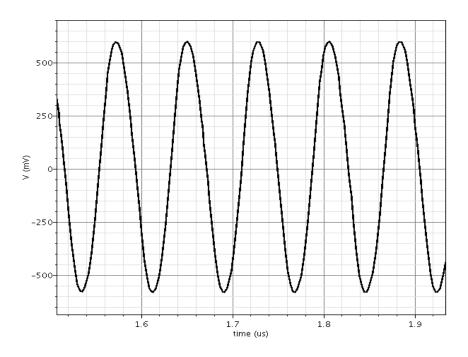

a frequency of 100 kHz. The passive components  $R_1$  = 17 k $\Omega$ ,  $R_2$  = 1.7 k $\Omega$  and C = 1 nF were used for the simulation. For selecting the passive component values for the second circuit shown in Fig. 3.9, followed the same procedure as stated to select the passive component values in the first square waveform generator circuit. For example, if  $f_o$  is chosen as 100 kHz, the circuit parameters are selected as C = 1nF,  $R_1 = 17$  k $\Omega$ , and  $R_2 = R_{2f} = R_{2n} = 1.7$  k $\Omega$ . The simulated output waveform for the circuit in Fig. 3.9 is shown in Fig. 3.11.

Fig. 3.11 Simulation result of the square waveform generator circuit in Fig. 3.9

The resistors  $R_{2f}$  and  $R_{2n}$  are varied independently to vary the on-duty and off-duty cycles of the output square waveform.

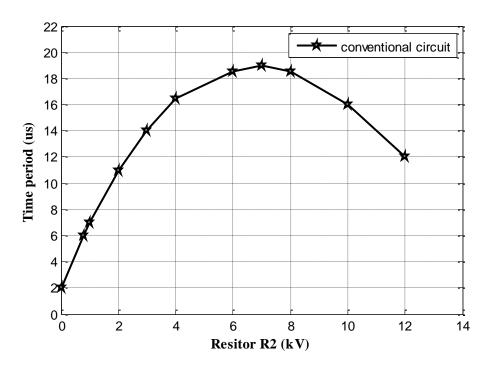

#### 3.3.2 DISCUSSIONS AND CONCLUSIONS

The proposed circuits in [45] are simpler than the traditional voltage-mode square waveform generators. From Fig. 3.10, it can be seen that the on-duty and off-duty cycles are not same for the first proposed circuit in Fig. 3.7. Small percentage of error present between the on-duty and off-duty cycles. For the second circuit shown in Fig. 3.9, the capacitor value is slightly adjusted to fine tune the output square wave frequency. For the 60% on-duty cycle,  $R_{2n}$  is larger than the  $R_{2f}$ . The capacitor voltage increases to a smaller  $V_{TH}$  with an even slower charging rate in the on-period. The minimum frequency range of the square waveform circuits in Fig. 3.7 and 3.8 is

limited by the values of the passive components connected to the circuits, mainly the capacitor. Large value of capacitor makes lower output frequency.

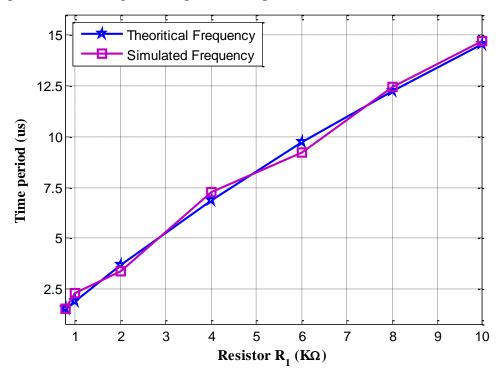

The highest frequency at the output terminal is limited due to the slew-rate of the active device. The highest output frequency is around several MHz. However, the circuit has the advantage of less passive components, but it makes a non-linear variation of the time period with respect to the resistor  $R_2$  and  $R_1$  value sholud be larger than  $R_2$  value to produce oscillations. The Fig. 3.12 shows the non-linear variation of time period with respect to the resistor  $R_2$ . For tuning the resistor  $R_2$ , passive components  $C = 1nF R_1 = 18k\Omega$  were chosen and  $R_2$  was varied from  $200\Omega$  to  $18 \ k\Omega$ . Moreover, the circuits proposed in [45] consume large amount of power with a supply voltage of  $\pm$  15 V.

Fig. 3.12 Variation of time period for the square waveform generator circuit shown in Fig. 3.9

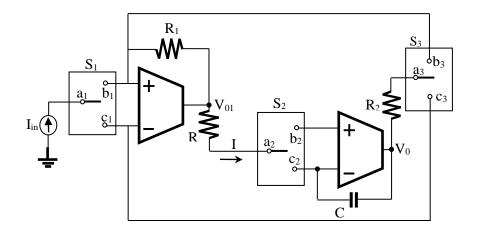

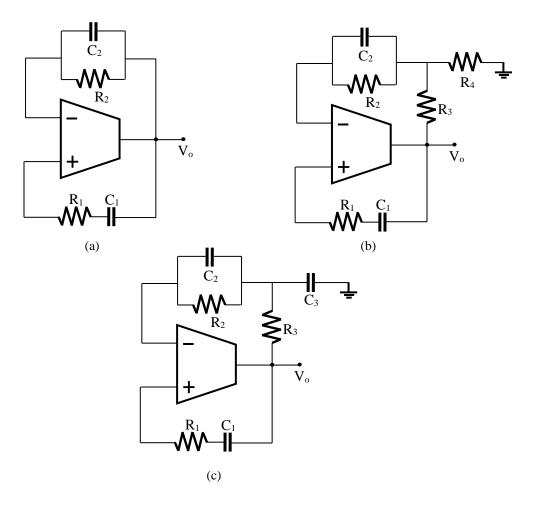

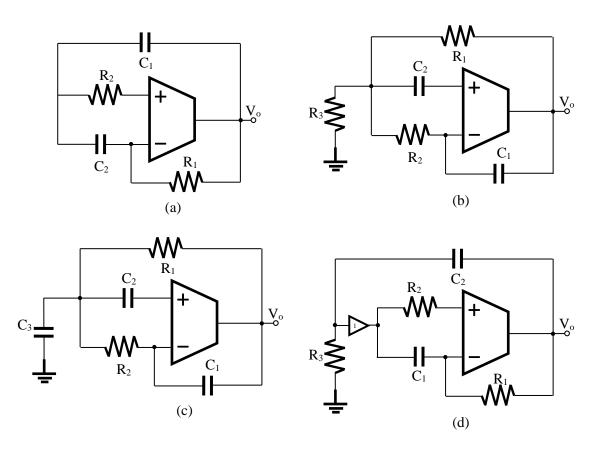

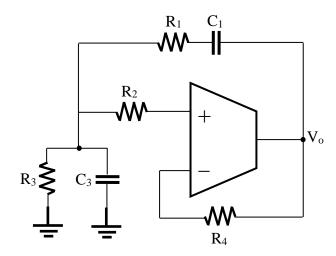

## 3.4 OTRA BASED SQUARE/TRIANGULAR WAVEFORM GENERATOR

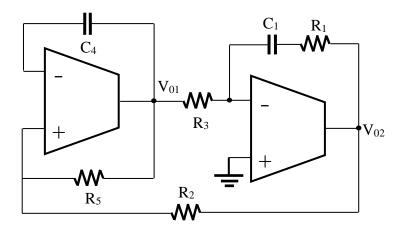

The OTRA based square/triangle waveform generator was proposed by Y. K. Lo *et al.*, in the year 2007 [46]. The circuit was implemented with two OTRAs, three switches and a few passive components. The circuit proposed in [46] has an advantage of producing both inverting and non-inverting mode of operations. The OTRA based square/triangle waveform generator is shown in Fig. 3.13. The operation

of the circuit can be explained as follows: for inverting mode operation the switches a2 is connected to c2 and a3 is connected to b3. For non-inverting mode operation the switches are connected as; a2 is connected b2 and a3 is connected to c3. The expected output waveform is shown in Fig. 3.14.

Fig. 3.13 OTRA based square/triangle waveform generator

Fig. 3.14 Expected output waveform from the circuit in Fig. 3.13

From the Fig. 3.14, the output is at negative saturation level  $L^-$ . The saturation current I, flows through the resistor R and C, this makes  $V_{02}$  to increase linearly.

$$I = \frac{V_{01}(t)}{R} = \frac{L^{-}}{R} = C\frac{dV_{02}}{dt}$$

(3.33)

This state continues until  $V_{02}$  reaches the upper threshold voltages  $V_{TH}$ . The upper threshold voltage can be derived by making inverting and non-inverting currents equal.

$$V_{TH} = R_2 I_{in} + \frac{R_2}{R_1} L^+ \tag{3.34}$$

When al is connected to b1,

$$V_{TH} = -R_2 I_{in} + \frac{R_2}{R_1} L^+ \tag{3.35}$$

Similarly, for lower threshold voltage V<sub>TL</sub>,

$$V_{TL} = R_2 I_{in} - \frac{R_2}{R_1} L^+ \tag{3.36}$$

$$V_{TL} = -R_2 I_{in} - \frac{R_2}{R_1} L^+ \tag{3.37}$$

The on-duty and off-duty cycles time period can be derived from the equations (3.34)-(3.37).

$$T_1 = 2RC \frac{R_2}{R_1} {(3.38)}$$

and for off-duty cycle,

$$T_2 = 2RC \frac{R_2}{R_1} = T_{off} (3.39)$$

The oscillation frequency is given by,

$$f = \frac{1}{4RC\left(\frac{R_2}{R_1}\right)} \tag{3.40}$$

#### 3.4.1 SIMULATION RESULTS

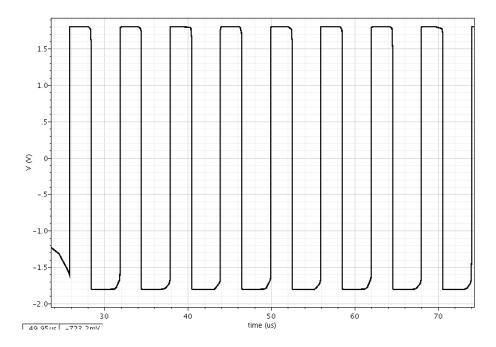

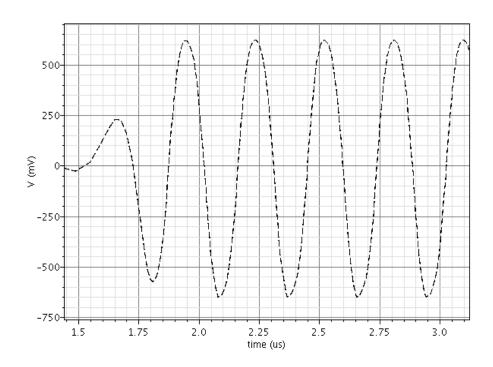

The circuit shown in Fig. 3.13 was simulated using Cadence Spectre simulation model parameters. The simulated square/triangular waveform is shown in Fig. 3.15.

#### 3.4.2 DISCUSSIONS AND CONCLUSIONS

The equation (3.40) is useful to facilitate the design of square/triangular waveform generator shown in Fig. 3.13. The oscillation frequency is specified first, and then the ratio  $R_2/R_1$  is found from equation (3.40) for an arbitrarily chosen capacitor C and resistor R values. The circuit has an advantage of producing both inverting and non-inverting output waveforms. The circuit presented in [46] is

successfully eliminated the errors presented in voltage-mode square/triangle waveform generator, specifically frequency and amplitude are dependent.

Fig. 3.15 Simulated output waveform from the circuit in Fig. 3.13

The minimum and maximum frequency range of the circuit is from kHz to few MHz. The minimum frequency is limited by the capacitor value and the maximum frequency is limited by the slew rate of the OTRA. However, the circuit shown in Fig. 3.13 is complex with three switches, two OTRAs and four passive components. Moreover, the circuit requires external current source I to adjust the DC level of the output waveform. The operation of the circuit is also complex with the switching positions of three switches. The circuit consume high power to operate with two OTRAs, three switches and four passive components.

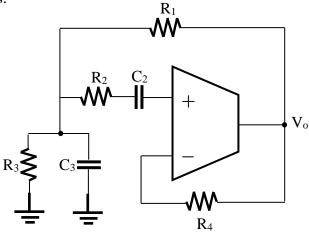

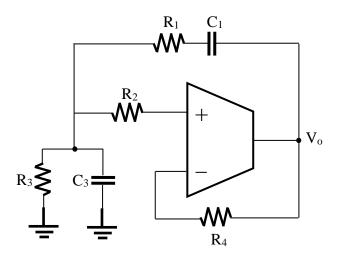

#### 3.5 OTRA BASED SINUSOIDAL OSCILLATORS

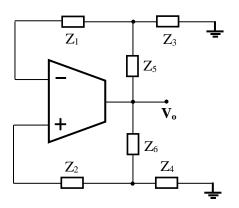

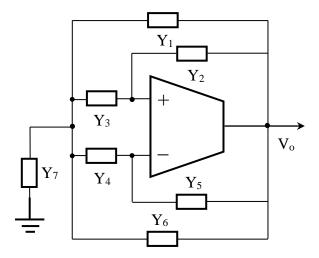

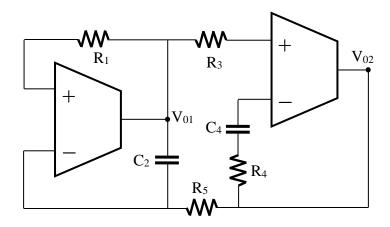

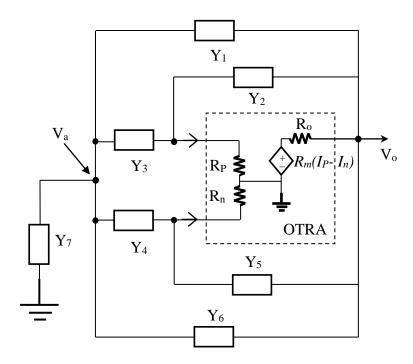

The first OTRA based sinusoidal waveform generator was proposed by K. N. Salama *et al.*, in the year 2000 [50]. Seven new sinusoidal oscillator designs are reported in [50]. In this paper, three oscillator circuits are realized from a generalized configuration using single OTRA and four sinusoidal oscillator circuits are designed using two OTRAs with a few passive components. The generalized configuration to realise several sinusoidal oscillators using single OTRA is shown in Fig. 3.16.

Fig. 3.16 OTRA based generalized configuration.

Fig. 3.17 Oscillators realized from the generalized configuration in Fig. 3.16

Assuming the OTRA used in the generalized configuration is ideal; the characteristic equation for the generalized configuration is by:

$$Z_2 + Z_5 \left(1 + \frac{Z_2}{Z_3}\right) = Z_1 + Z_6 \left(1 + \frac{Z_1}{Z_4}\right)$$

(3.41)

Several oscillator circuits can be realized from the generalized configuration. Three special cases are shown in the Fig. 3.17. Minimum passive component oscillator that can be realized from the generalized configuration is show in Fig. 3.17 (a). The circuit shown in Fig. 3.17 (a) requires two capacitors and two resistors to produce the oscillation. The condition of oscillation and frequency of oscillation are given by

$$\frac{R_1}{R_2} + \frac{C_2}{C_1} = 1 \tag{3.42}$$

$$\omega_o = \frac{1}{\sqrt{C_1 C_2 R_1 R_2}} \tag{3.43}$$

From equations (3.42) and (3.43), it is clear that the condition of oscillation and frequency of oscillation cannot be controlled independently from the circuit in Fig. 3.17 (a). The oscillator circuits shown in Fig. 3.17 (b) & (c) are able to control the condition of oscillation and frequency of oscillation independently. The characteristic equations for the circuits shown in Fig. 3.17 (b) & (c) can be derived from the generalized equation (3.41). For the oscillator circuit in Fig. 3.17 (b), the grounded resistor R<sub>4</sub> is used to control the condition of oscillation without affecting the frequency of oscillation. From the equations (3.46) and (3.47), the capacitor C<sub>3</sub> in Fig. 3.17 (c) is used to control the frequency without affecting the condition of oscillation. Four quadrature oscillators using two OTRAs are shown in Fig. 3.18 [50].

For Fig. 3.17 (b)

$$\frac{R_1}{R_2} + \frac{C_2}{C_1} = 1 + \frac{R_3}{R_2} + \frac{R_3}{R_4}$$

(3.44)

$$\omega_o = \frac{1}{\sqrt{C_1 C_2 R_1 R_2 \left(1 - \frac{R_3}{R_1}\right)}}$$

(3.45)

For Fig. 3.17(c)

$$\frac{R_1}{R_2} + \frac{C_2}{C_1} = 1 + \frac{R_3}{R_2} \tag{3.46}$$

Fig. 3.18 Sinusoidal oscillators using two OTRAs

$$\omega_{o} = \frac{1}{\sqrt{C_{1}C_{2}R_{1}R_{2}\left(1 - \frac{R_{3}}{R_{1}}\left(1 + \frac{C_{3}}{C_{2}}\right)\right)}}$$

(3.47)

These oscillator circuits are constructed with two capacitors and four or five resistors. All the circuits shown in Fig. 3.18 are able to control the frequency of oscillation and condition of oscillation independently. The condition of oscillation and frequency of oscillation for these circuits are derived from the state matrix of the corresponding circuits.

$$C_1 R_3 = C_2 R_4 \tag{3.48}$$

$$\omega_o = \frac{1}{\sqrt{C_1 C_2 R_1 R_2 \left(1 - \frac{R_1 R_2}{R_3 R_4}\right)}}$$

(3.49)

The equations (3.48) and (3.49) are derived from the state matrix shown below for the circuit in Fig. 3.18 (a).

$$\begin{bmatrix} \frac{dV_1}{dt} \\ \frac{dV_2}{dt} \end{bmatrix} = \begin{bmatrix} -\frac{1}{C_1 R_3} & \frac{1}{C_1 R_1} \\ -\frac{C_2}{R_2} & \frac{1}{C_2 R_4} \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}$$

(3.50)

The condition of oscillation and frequency of oscillation is same for the circuits in Figs. 3.18 (b) and (c).

$$R_3 = R_4 \tag{3.51}$$

$$\omega_o = \frac{1}{\sqrt{C_1 C_2 R_1 R_2}} \tag{3.52}$$

For producing oscillations in the circuit shown in Fig. 3.18 (d), it requires, two OTRAs, four resistors and two capacitors. The condition of oscillation and frequency of oscillation is given in equations (3.53) and (3.54).

$$R_3 = 3R \tag{3.53}$$

$$\omega_o = \frac{3}{\sqrt{C_1 C_2 R_1 R_2}} \tag{3.54}$$

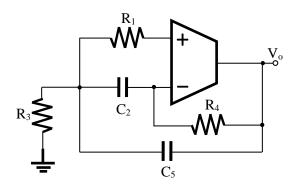

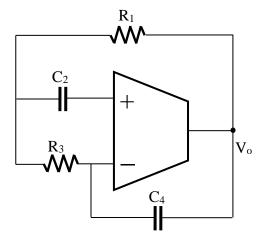

A novel single resistance controlled sinusoidal oscillator employing single OTRA was proposed by U. Cam in the year 2002 [51]. The circuit proposed in [51] is simpler than the circuits in Fig. 3.17.

Fig. 3.19 SRCO using single OTRA

The circuit diagram of the oscillator is shown in Fig. 3.19. Routine analysis for the above circuit gives the following equations.

$$C_2G_4 + C_5G_4 = C_5G_1 \tag{3.55}$$

$$f = \frac{1}{2\pi} \sqrt{\frac{G_4(G_1 + G_3)}{C_2 C_5}}$$

(3.56)